© National Instruments

|

2-17

DI Change Detection Applications

The DIO change detection circuitry can interrupt a user program when one of several DIO

signals changes state.

You also can use the output of the DIO change detection circuitry to trigger a DI or counter

acquisition on the logical OR of several digital signals. By routing the Change Detection Event

signal to a counter, the relative time between bus changes can be captured.

The Change Detection Event signal can be used to trigger DO or counter generations.

Digital Filtering

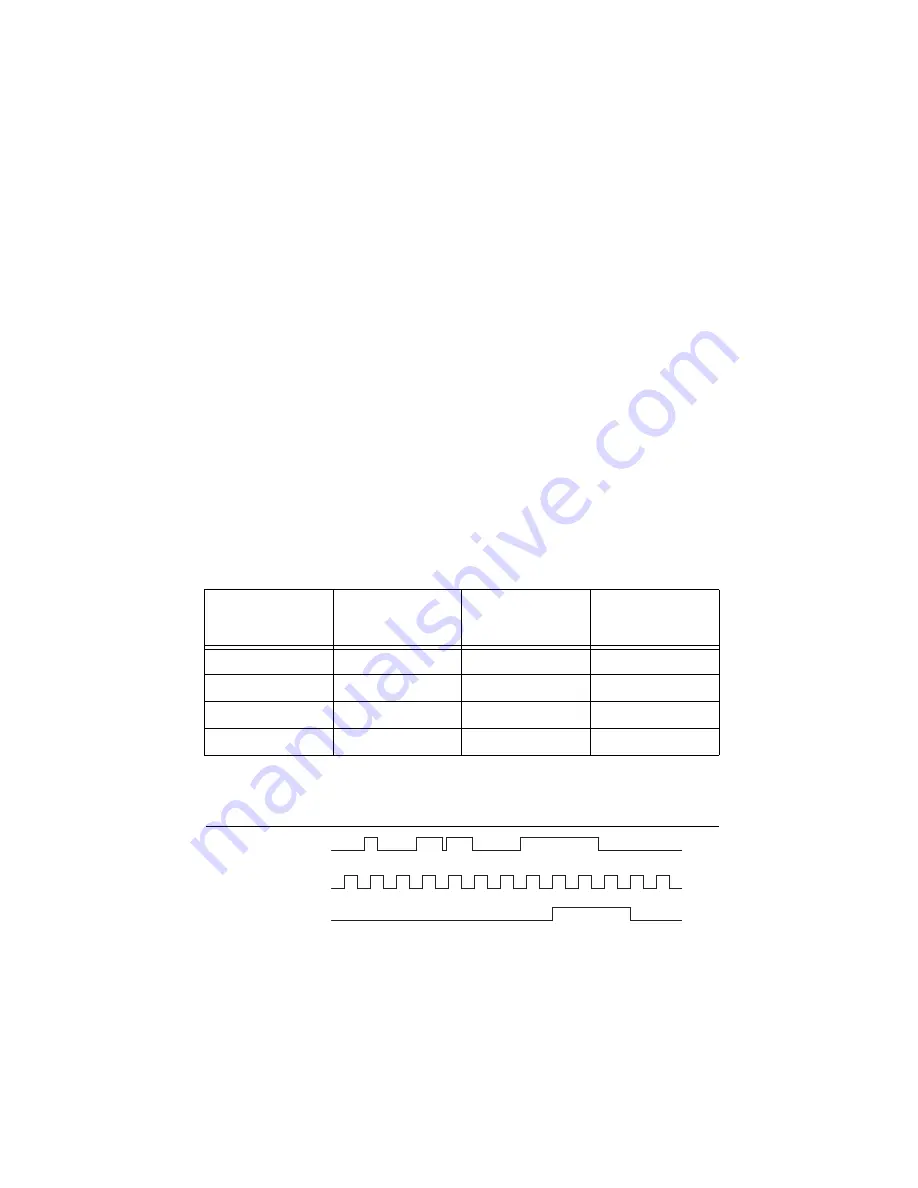

A programmable debouncing filter can be enabled on each digital line on Port 0. When the filters

are enabled, the device samples the input on each rising edge of a filter clock. The device divides

down the onboard 100 MHz or 100 kHz clocks to generate the filter clock. The following is an

example of low-to-high transitions of the input signal. High-to-low transitions work similarly.

Assume that an input terminal has been low for a long time. The input terminal then changes

from low-to-high, but glitches several times. When the filter clock has sampled the signal high

on two consecutive edges and the signal remained stable in between, the low-to-high transition

is propagated to the rest of the circuit.

The filter setting for each input can be configured independently. On power up, the filters are

disabled. Figure 2-13 shows an example of a low-to-high transition on an input.

Figure 2-13.

Input Low-to-High Transition

Table 2-3.

Filters

Filter Settings

Filter Clocks

Pulse Width

Guaranteed to

Pass Filter

Pulse Width

Guaranteed to Not

Pass Filter

Short

12.5 MHz

160 ns

80 ns

Medium

195/3125 kHz

10.24

μ

s

5.12

μ

s

High

390.625 Hz

5.12 ms

2.56 ms

None

—

—

—

Digit

a

l Inp

u

t P0.

x

Filter Clock

Filtered Inp

u

t

1

1

2

1

1

2

1