© National Instruments

|

5-39

Other Counter Features

The following sections list the other counter features available on the cDAQ chassis.

Cascading Counters

You can internally route the Counter n Internal Output and Counter n TC signals of each counter

to the Gate inputs of the other counter. By cascading two counters together, you can effectively

create a 64-bit counter. By cascading counters, you also can enable other applications. For

example, to improve the accuracy of frequency measurements, use reciprocal frequency

measurement, as described in the

Large Range of Frequencies with Two Counters

Prescaling

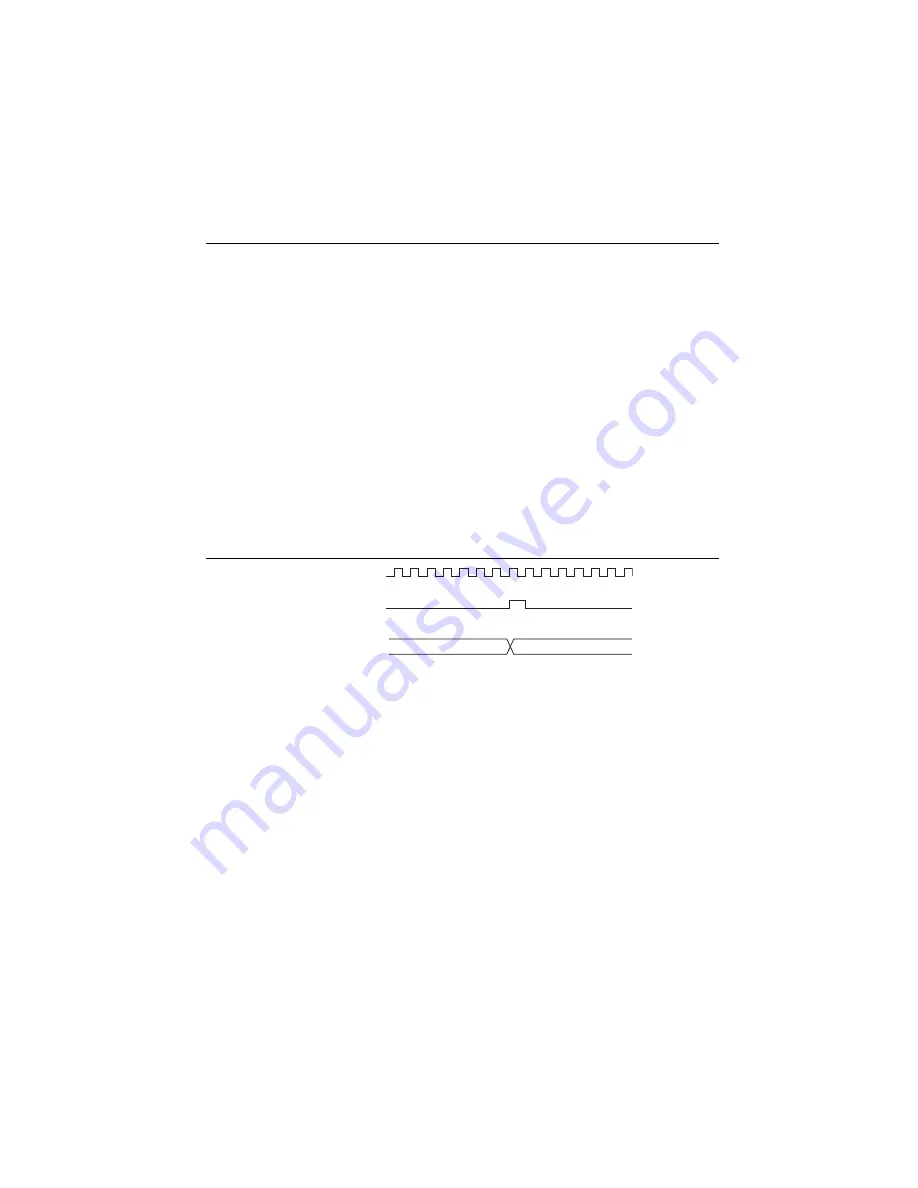

Prescaling allows the counter to count a signal that is faster than the maximum timebase of the

counter. The cDAQ chassis offers 8X and 2X prescaling on each counter (prescaling can be

disabled). Each prescaler consists of a small, simple counter that counts to eight (or two) and

rolls over. This counter can run faster than the larger counters, which simply count the rollovers

of this smaller counter. Thus, the prescaler acts as a frequency divider on the Source and puts

out a frequency that is one-eighth (or one-half) of what it is accepting as shown in Figure 5-37.

Figure 5-37.

Prescaling

Prescaling is intended to be used for frequency measurement where the measurement is made on

a continuous, repetitive signal. The prescaling counter cannot be read; therefore, you cannot

determine how many edges have occurred since the previous rollover. Prescaling can be used for

event counting provided it is acceptable to have an error of up to seven (or one) ticks. Prescaling

can be used when the counter Source is an external signal. Prescaling is not available if the

counter Source is one of the internal timebases (80MHzTimebase, 20MHzTimebase, or

100kHzTimebase).

Synchronization Modes

The 32-bit counter counts up or down synchronously with the Source signal. The Gate signal and

other counter inputs are asynchronous to the Source signal, so the cDAQ chassis synchronizes

these signals before presenting them to the internal counter.

Depending on how you configure your chassis, the cDAQ chassis uses one of two

synchronization methods:

•

•

External or Internal Source Less than 20 MHz

Extern

a

l

S

ign

a

l

Co

u

nter V

a

l

u

e

Pre

s

c

a

ler Rollover

(U

s

ed

as

S

o

u

rce

b

y Co

u

nter)

0

1