4-8

Computer Group Literature Center Web Site

Functional Description

4

PCI Bus 1

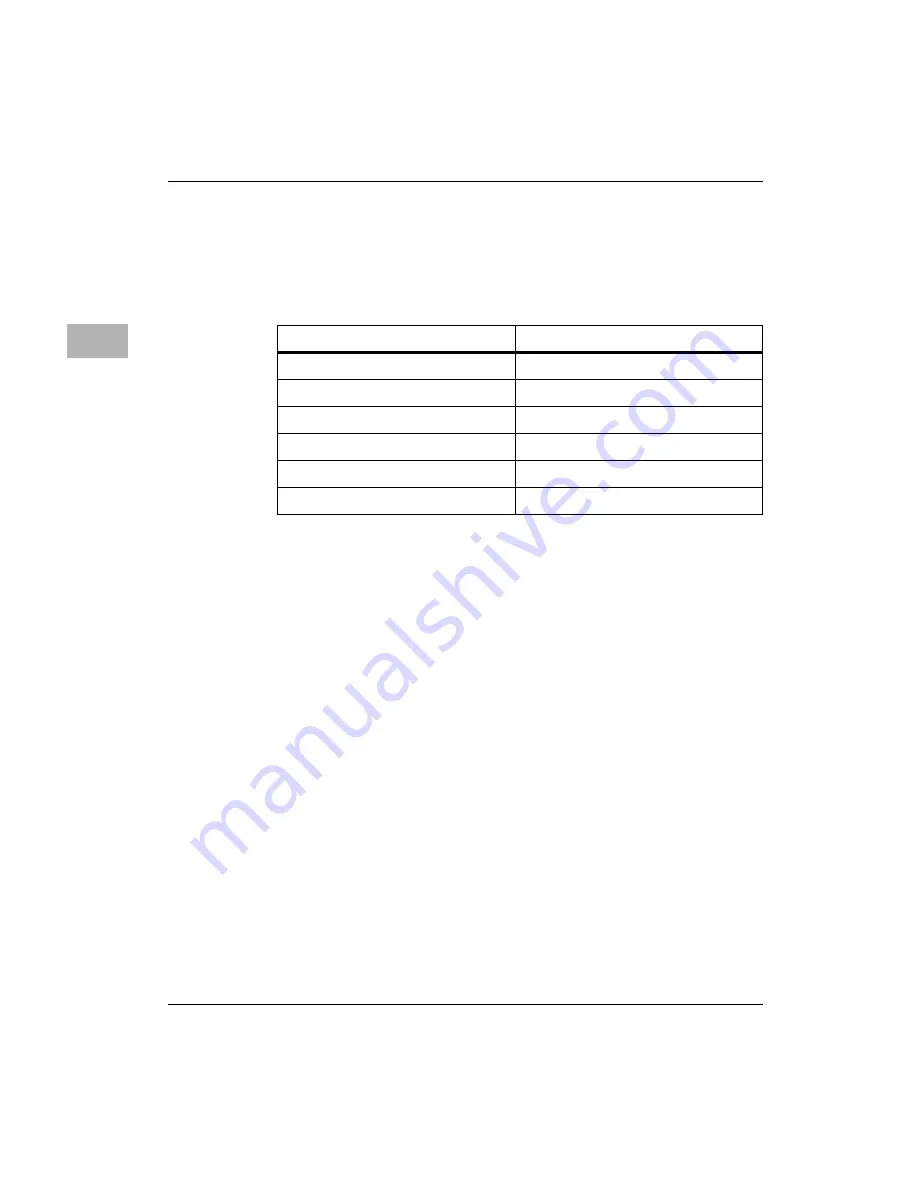

The PCI request/arbitration assignments for the PCI bus 1 are as follows:

Table 4-3. PCI Bus 1 Arbitration Assignments

PCI Bus Request

PCI Master(s)

Request 0

Onboard LAN 82546EB

Request 1

PMC slot 1 (1st REQ)

Request 2

PMC slot 1 (2nd REQ)

Request 3

PMC slot 2

Request 4

None

Request 5

None