DS3234

Extremely Accurate SPI Bus RTC

with Integrated Crystal and SRAM

Maxim Integrated | 19

www.maximintegrated.com

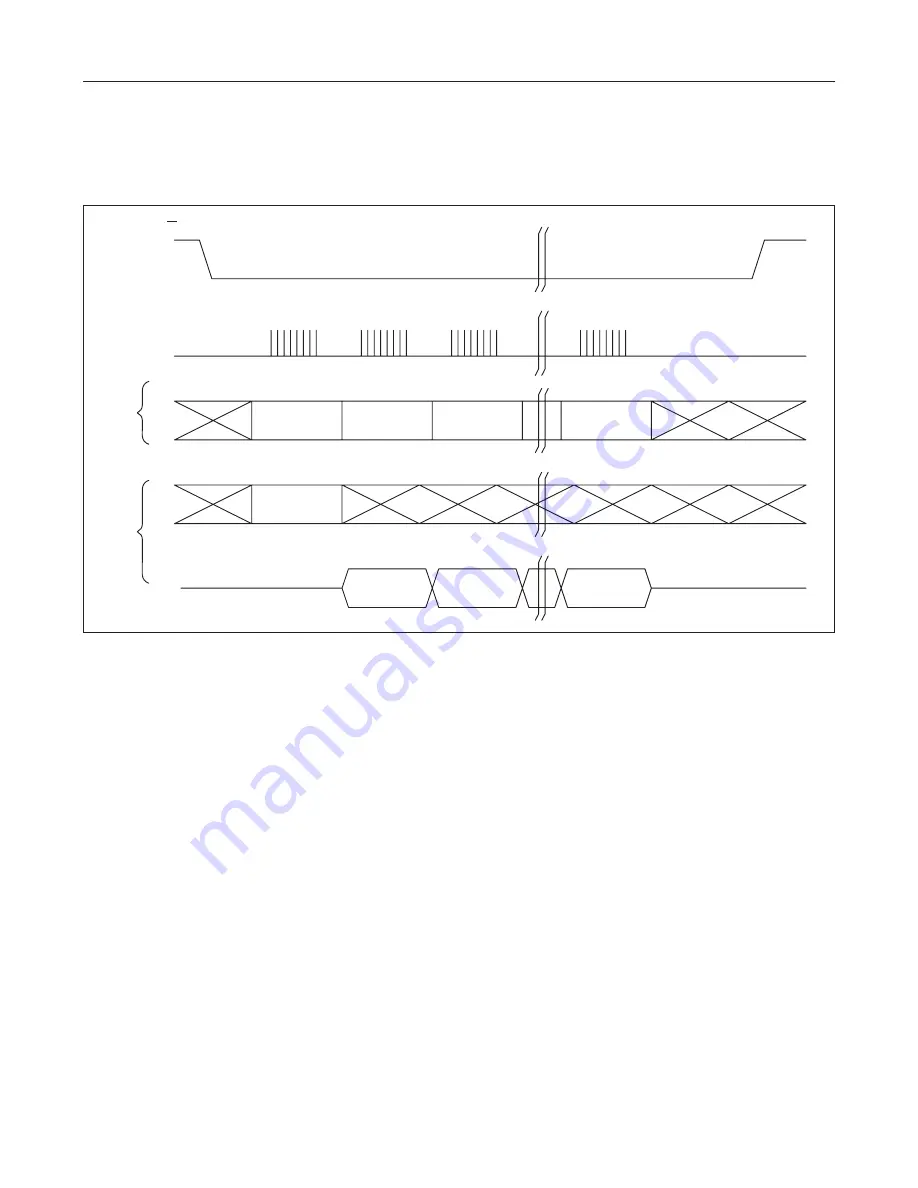

Data transfers can occur one byte at a time or in multi-

ple-byte burst mode. After

CS

is driven low, an address

is written to the DS3234. After the address, one or more

data bytes can be written or read. For a single-byte

transfer, one byte is read or written and then

CS

is dri-

ven high. For a multiple-byte transfer, however, multiple

bytes can be read or written after the address has been

written (Figure 5). Each read or write cycle causes the

RTC register address to automatically increment, which

continues until the device is disabled. The address

wraps to 00h after incrementing to 13h (during a read)

and wraps to 80h after incrementing to 93h (during a

write). An updated copy of the time is loaded into the

user buffers upon the falling edge of

CS

and each time

the address pointer increments from 13h to 00h.

Because the internal and user copies of the time are

only synchronized on these two events, an alarm condi-

tion can occur internally and activate the

INT/

SQW pin

independently of the user data.

If the SRAM is accessed by reading (address 19h) or

writing (address 99h) the SRAM data register, the con-

tents of the SRAM address register are automatically

incremented after the first access, and all data cycles

will use the SRAM data register.

Handling, PC Board Layout,

and Assembly

The DS3234 package contains a quartz tuning-fork

crystal. Pick-and-place equipment can be used, but

precautions should be taken to ensure that excessive

shock and vibration are avoided. Exposure to reflow is

limited to 2 times maximum. Ultrasonic cleaning should

be avoided to prevent damage to the crystal.

Avoid running signal traces under the package, unless

a ground plane is placed between the package and the

signal line. All N.C. (no connect) pins must be connect-

ed to ground.

CS

SCLK

DIN

DOUT

HIGH IMPEDANCE

ADDRESS

BYTE

ADDRESS

BYTE

DATA BYTE 0

DATA BYTE 1

DIN

DATA BYTE N

DATA

BYTE 0

DATA

BYTE 1

DATA

BYTE N

WRITE

READ

Figure 5. SPI Multiple-Byte Burst Transfer