TK-2317

24

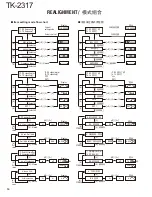

3-3. APC Circuit

The APC circuit always monitors the current flowing

through the drive amplifi er (Q204) and the RF power ampli-

fi er (Q205) and keeps a constant current. The voltage drop

at R307, R309 and R310 is caused by the current fl owing

through the RF fi nal amplifi er. This voltage is applied to the

differential amplifi er IC301 (1/2).

IC301 (2/2) compares the output voltage of IC301 (1/2)

with the reference voltage from IC811. The output of IC301

(2/2) controls the VG of the RF power amplifi er and the drive

amplifi er to make both voltages the same.

The change of power high/low is carried out by the

change of the reference voltage.

Fig. 5 Driver and fi nal amplifi er and APC circuit

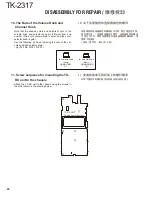

4. Frequency Synthesizer Unit

4-1. Frequency synthesizer

The frequency synthesizer consists of the TCXO (X1),

VCO, PLL-IC (IC1), and buffer amplifi ers.

The TCXO generates 16.8MHz. The frequency stability is

1.5ppm within the temperature range of –30°C to +60°C. The

frequency tuning and modulation of the TCXO are done to

apply voltage to pin 1 of the TCXO. The output of the TCXO

is applied to pin 10 of PLL-IC.

The VCO consists of 2 VCO and covers a dual range of

136.00~174.00MHz and 185.95~223.95MHz. The VCO gen-

erates 185.95~223.95MHz for providing the fi rst local signal

for reception. The operating frequency is generated by Q5 in

transmitting mode and Q4 in receiving mode. The oscillation

frequency is controlled by applying the VCO control voltage,

obtained from the phase comparator (IC1) to the variable ca-

pacitance diodes (D4, D6, D8 and D9 in transmitting mode

and D10 and D12 in receiving mode)

The TX/RX pin of IC820 goes “high” in transmitting mode,

causing Q7 and Q4 to turn off, and Q5 turn on. The TX/RX

pin goes “low” in receiving mode.

The output from Q4 and Q5 are amplifi ed by a buffer am-

plifi er (Q8) and Q2, and then sent to the PLL-IC.

The PLL-IC consists of a prescaler, reference divider,

ANT

RF FINAL

AMP

ANT

SW

LPF

From

T/R SW

(D18)

D201,202

+B

PC/BPF2

(IC811)

RF

AMP

Q201

Q205

DRIVE

AMP

Q204

VDD

VG

Pre-DRIVE

AMP

Q203

IC301

(1/2)

IC301

(2/2)

R307

R309

R310

CIRCUIT DESCRIPTION /

电路说明

图 5 驱动器和终端放大器电路和自动功率控制 (APC) 电路

3-3. 自动功率控制 (APC) 电路

APC 电路一直监视通过驱动放大器 (Q204) 和射频功率放大

器 ( Q205) 的电流并保持电流稳定。经过射频功率放大器的电

流的变化会引起 R307、R309 和 R310 的电压降低,此电压送

到差分放大器 IC301(1/2)。

I C301(2/2) 将 I C301(1/2) 的输出电压与来自 I C811 的参

考电压进行比较。I C301(2/2) 的输出电压控制射频功率放大

器、驱动放大器、预驱动放大器的 VG,使电压保持一致。

功率高 / 低的变化是通过变更参考电压来实现的。

4. 频率合成器电路

4-1. 频率合成器

频率合成器由 TCXO(X1)、VCO、PLL IC(IC1) 和缓冲放大

器组成。

TCXO 产生 16.8MHz 的频率。在温度为 -30 ~ +60℃的范围内,

频率的稳定性为 1.5ppm。进行频率调谐和 TCXO 调制,以便给

TCXO 的针脚 1 提供电压。TCXO 的输出加在 PLL IC 的针脚 10 上。

VCO 由 2VCO 组 成, 并 且 覆 盖 了 136.00 ~ 174.00M H z 和

185.95 ~ 223.95MHz 双波段。VCO 产生 185.95 ~ 223.95MHz

的频率,以提供接收的第一个本振信号。发射模式时,操作

频率由 Q5 产生,而接收模式时,操作频率由 Q4 产生。振荡

频率由加在 VCO 上的控制电压控制,控制电压从可变电容二

极管 ( 在发射模式是 D6 和 D9,在接收模式是 D10 和 D12) 的

相位比较器 (IC1) 处获得。

IC820 的 TX/RX 针脚在接收模式时为“低”电位,使 Q7 和

Q4 打开。TX/RX 针脚在发射模式时为“高”电位,使 Q5 导通。

Q4 和 Q5 的输出由缓冲放大器 (Q8) 和 Q2 放大,然后发送到

PLL IC。

PLL IC 由预计数器、基准除法器、相位比较器、电荷泵组

成 ( PLL 电路的频率步长为 5kHz 或 6.25kHz )。PLL IC 的针

脚 10 和 17 的输入信号下分成 5k H z 或 6.25k H z,并在相位比

较器处进行比较。相位比较器的脉冲输出信号加在电荷泵上,

并转换成环路滤波器 ( LPF ) 的 DC 信号。DC 信号加在 VCO 的

CV 上并锁定,使 VCO 的频率恒定。