NX-720H(G)/720H

13

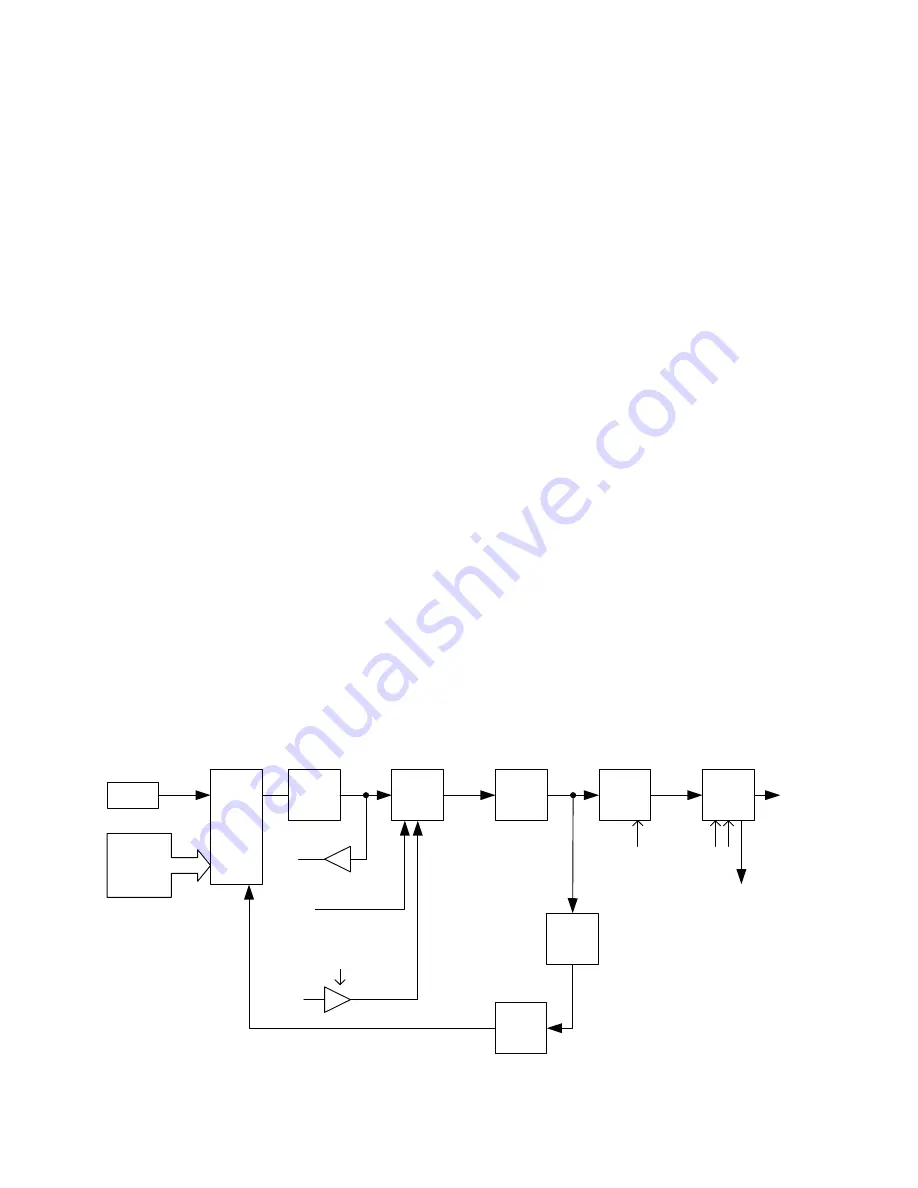

Fig. 6 PLL circuit

CIRCUIT DESCRIPTION

5. PLL Frequency Synthesizer

5-1. TCXO (X1)

The TCXO (X1) generates a reference frequency of

16.8MHz for the PLL frequency synthesizer. This reference

frequency is applied to pin 9 of the PLL IC (IC2) and is con-

nected to the IF circuit as a 2nd local signal through the Tri-

pler.

The frequency adjustment is achieved by switching the

ratio of the dividing frequency. The resolution of the adjusting

frequency is approximately 4Hz.

5-2. VCO

There is an RX VCO and a TX VCO.

The TX VCO (Q7) generates a transmit carrier and the

RX VCO (Q6) generates the 1st local signal. For the VCO

oscillation frequency, the transmit carrier is 136 to 174 MHz

and the 1st local signal is 185.95 to 223.95MHz.

The VCO oscillation frequency is determined by one sys-

tem of operation switching terminal "T/R" and two systems

of voltage control terminals "CV" and "ASSIST".

The operation switching terminal, "T/R", is controlled by

the control line (/T_R) output from the ASIC (IC507). When

the /T_R logic is low, the VCO outputs the transmit carrier

and when it is high, it outputs the 1st local receive signal.

The voltage control terminals, "CV" and "ASSIST", are

controlled by the PLL IC (IC2) and ASIC (IC507) and the

output frequency changes continuously according to the

applied voltage. For the modulation input terminal, "VCO_

MOD", the output frequency changes according to the ap-

plied voltage. This is used to modulate the VCO output.

"VCO_MOD" works only when "/T_R" is low.

5-3. PLL IC (IC2)

The PLL IC compares the differences in phases of the

VCO oscillation frequency and the TCXO reference fre-

quency, returns the difference to the VCO CV terminal and

realizes the "Phase Locked Loop" for the return control. This

allows the VCO oscillation frequency to accurately match

(lock) the desired frequency.

When the frequency is controlled by the PLL , the fre-

quency convergence time increases as the frequency dif-

ference increases when the set frequency is changed. To

supplement this, the ASIC (IC507) is used before control by

the PLL IC to bring the VCO oscillation frequency close to

the desired frequency. As a result, the VCO CV voltage does

not change and is always stable at approximately 2.5V.

The desired frequency is set for the PLL IC by the ASIC

(IC507) through the 3-line "SDO1", "P_SCK1", "/PCS_RF"

serial bus. Whether the PLL IC is locked or not is monitored

by the ASIC through the “PLD” signal line. If the VCO is not

the desired frequency (unlocked), the "PLD" logic is low.

The modulation signal of the Low-speed-Data is applied

to pin 23 of the PLL IC (IC2).

The modulation signal that is digital data of a sampling

frequency of 96 kHz is set for the PLL IC by the DSP (IC502)

through the “PLL_MOD” line.

5-4. Local Switch (D16, D17)

The connection destination of the signal output from the

buffer amplifi er (Q11) is changed with the diode switch (D17)

that is controlled by the transmission power supply, HSW,

and the diode switch (D16) that is controlled by the reception

power supply, 50R. If the HSW logic is high, it is connected

to a transmit-side drive (Q102). If the HSW logic is low, it is

connected to a receive-side mixer (Q202).

T/ R

SW

HSW

50

R

D16,17

RKS151KJ

BUFF

AMP

BUFF

AMP

Q11

Q10

2SC5108(Y)F

VCO

Q6,7 MCH3

9

14(7)-H

D4,5 1SV325F

D7,8,

9

,10,11,12 1SV282-F

D15 1SV282F

PLL

Loop

Filter

VCO MOD

ASSIST

CV

TCXO

X1 16.8MHz

SDO1

PCK_RF

/PCS RF

PLLMOD

IC2

SKY72310-362

IC3(2/2)

IC3(1/2)

BD7542FVM

BD7542FVM

50

CS

150C

to 1

st

MIXer

to TX stage

BPF

Doubler

Q5

2SC5108(Y)F

2SC5108(Y)F

Содержание Nexedge NX-720H

Страница 83: ...NX 720H G 720H 83 MEMO ...