KPCMCIA-12AIAOH User’s Manual

I/O Registers

C-15

Scan rate selection

Depending on the input mode and the gain selection, the analog front end may have different set-

tling times. To keep the best performance, the KPCMCIA-12AIAOH PC card allows you to

choose three different scanning rates by setting bit 2 and bit 3 while the start A/D command is

issued. The default scanning rate is 100kHz (bits 3 and 2 set to 00). Setting the bits to 01, selects

the 50kHz rate. Setting the bits to 10 selects 25kHz. Setting the bits to 11 is the same as 01.

It is recommended that the scan rate setting be issued together with the trigger/arm command, and

not changed during data acquisition. For example, writing 81H to the auxiliary control register

will start the data acquisition with the scan rate set to 100kHz (use 83H for 50kHz and 85H

for 25kHz).

D/A data port (base + 8, base + 9)

The D/A data port can be accessed either as a 16-bit word at base + 8 or as two consecutive bytes

at base + 8 (low byte) and base + 9 (high byte). The port is write only. For simplicity, the 16-bit

word is assumed in the following discussion.

Bits 12 to 15 select the D/A channel in which bits 13, 14, and 15 must all be set to 0, and bit 12

is either set at 0 to select D/A channel 0 or 1 to select D/A channel 1. Refer to Table C-15 for bit

definitions.

D/A channel output

Bits 0 to 11 specify the D/A channel data, which is always in 2’s complement format. The bipolar

D/A channel output ranges from -5 to +5V with corresponding code values from -2048 to 2047.

The actual D/A output voltage U (in volts) can be determined from the output code value C from

the following formula:

U = C*5 / 2048

Only the output of D/A channel 1 is used to set the analog trigger threshold. Refer to “Analog

trigger threshold” for more information.

D/A port interface

The data link between the D/A data port and the D/A converter is a serial link. A 16-bit buffer

register and a 16-bit shift register are in the port interface. On the other side of the link, an input

register and an output register are in each D/A channel of the D/A converter. The actual analog

output voltage is determined by the code value loaded into the output register as described in the

previous paragraph.

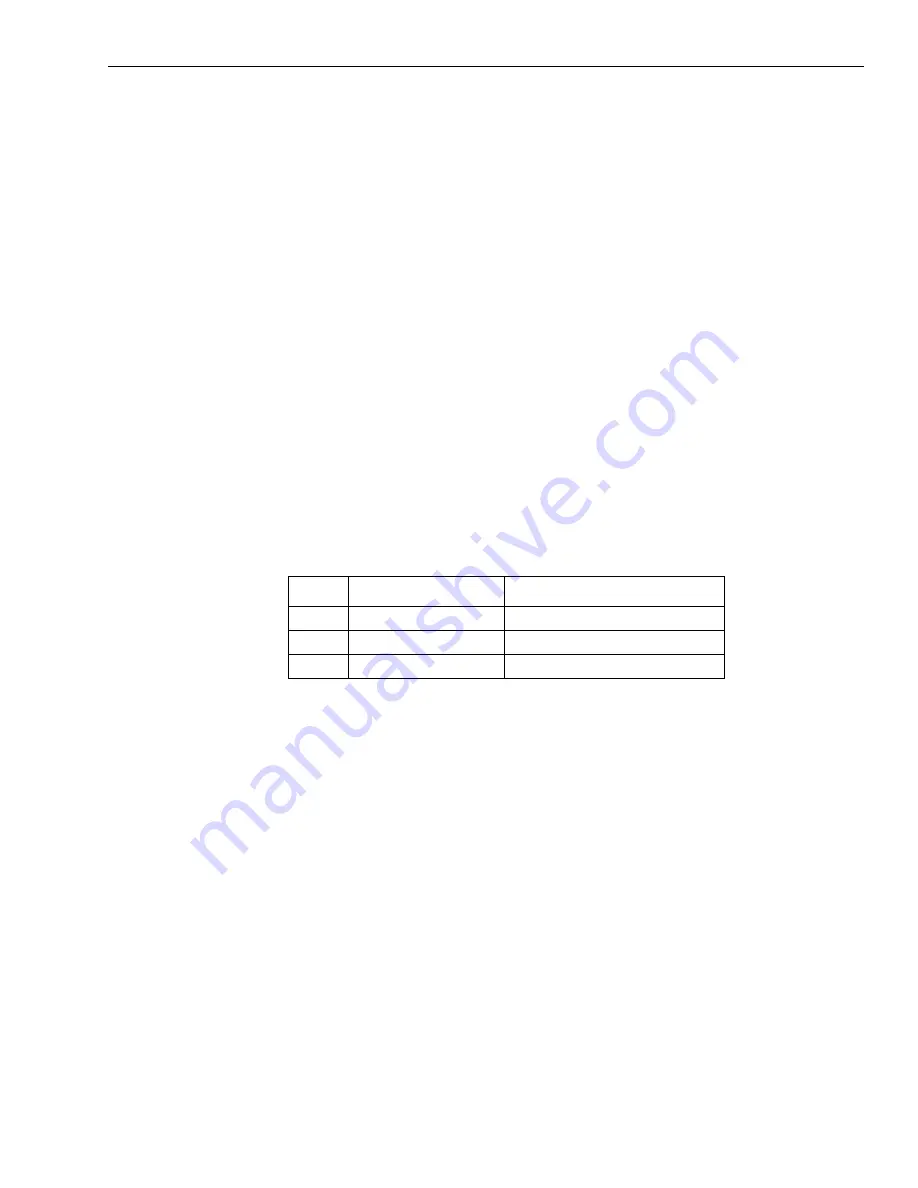

Table C-15

D/A data port bit definitions

Bits

Definition

Explanation

15-13

Reserved

as all 0

12

D/A channel selection

0 for channel 0, 1 for channel 1

11-0

D/A output code value

-2048..2047 in 2’s complement

Содержание KPCMCIA-12AIAOH

Страница 11: ...1 Introduction...

Страница 15: ...2 Installation...

Страница 17: ...3 Theory of Operation...

Страница 25: ...4 I O Connections...

Страница 28: ...5 Optional Accessories...

Страница 30: ...A Specifications...

Страница 33: ...B PCMCIA Interface...

Страница 36: ...C I O Registers...