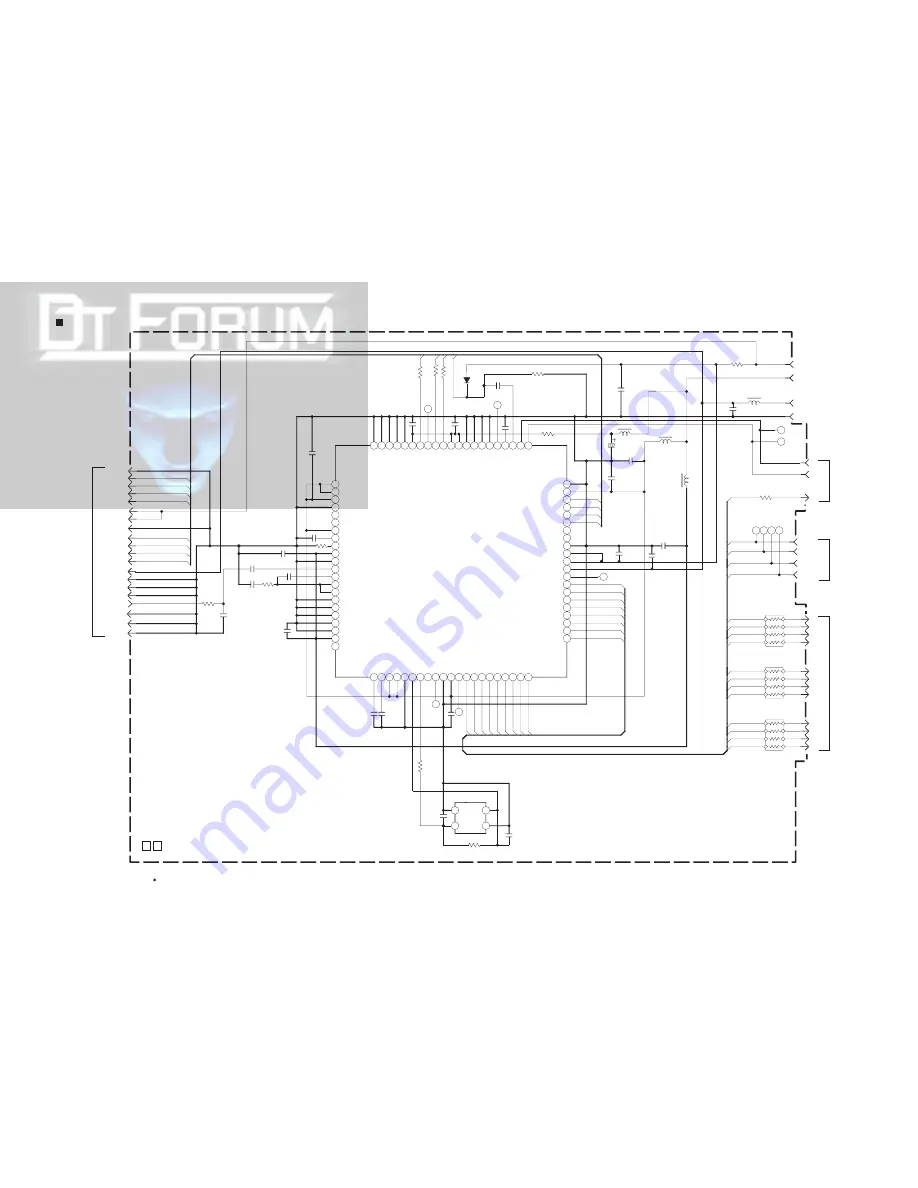

(No.YF219)2-17

2-18(No.YF219)

yf219_y30390001a_rev0.1

MAIN(CDS/TG)

1

0

IC4201

R2J45021/ABG

TO PARAGON

CAM_OUT

ADIN0_RA4201

ADIN1_RA4201

ADIN2_RA4201

ADIN3_RA4201

ADIN4_RA4202

CLKI_R4204

CDSTG_RST

ADIN11_RA4203

ADIN10_RA4203

ADIN8_RA4202

ADIN7_RA4203

ADIN6_RA4202

V3

V2

V1

OSC_O

CLKI

CLKI_R4204

REG_-7.5V

SUB

OSC_I

REG_2.8V_L4205

CCD_-7.5V

V4

CDSTG_CS

REG_2.8V

CAM_CLK

ADIN9_RA4203

ADIN11

ADIN10

ADIN5

ADIN6

ADIN8

ADIN4

ADIN3

ADIN0

ADIN1

ADIN1_RA4201

ADIN0_RA4201

ADIN3_RA4201

ADIN2_RA4201

ADIN5_RA4202

ADIN6_RA4202

ADIN8_RA4202

ADIN4_RA4202

ADIN9_RA4203

ADIN10_RA4203

ADIN11_RA4203

ADIN7_RA4203

REG_2.8V_L4203

REG_2.8V_L4204

CDSTG_RST

CAM_CLK

CAM_OUT

CDSTG_CS

VDIN

HDIN

ADIN5_RA4202

ADIN2

V2

V3

V4

RG

SUB

H2

H1

CCD_OUT

ADIN7

ADIN9

V1

H2

H1

RG

REG_15V

REG_15V_R4235

C4217

0.1

C4224

0.1

C4226

0.1

C4223

0.1

C4222

0.1

C4221

0.1

C4220

0.1

C4206

4.7/6.3V

C4205

4.7/6.3V

C4203

4.7/16V

C4214

0.1

C4213

1000p

C4227

0.1

C4212

15p

C4215

0.1

C4211

0.1

C4216

0.1

C4210

0.1

C4209

0.1

C4207

9p

C4218

0.1

C4208

9p

C4201

C4202

OPEN

C4204

22/6.3V

T

D4201

1SS355-X

X4201

GND

2

XOUT

3

GND

4

XIN

1

15

VRT

16

VRB

73

DVdd1

72

DVdd1

49

Test_i2

30

OSC_i

31

OSC_o

69

Test_o2

50

ADCK

22

DVss12

25

DVdd2

52

SDO

48

SCK

20

SDI

18

CS

23

D0

53

D1

24

D2

54

D3

79

D4

55

D5

56

D6

59

D7

26

D8

81

D9

27

D10

58

D11

61

Reset

62

CLK_o

51

ID

75

VL

19

VHH

82

VH

85

VM

76

V6

77

V5

78

V4

57

V2

80

V3

60

V1

32

DVdd3

33

DVss3

83

HD_I/O

84

VD_I/O

21

Sub

34

DLLC

74

MON

29

Scan

35

DVss5

64

DVss5

63

DVss5

36

DVdd5

37

DVdd5

1

H1

2

H2

39

HL

3

RG

4

DVdd4

66

DVss4

68

DVss4

5

DVss4

40

DVss4

67

DVss4

38

Vdr VDD

65

Vdr VDD

6

DVdd1

41

DVss1

42

Test_o1

44

Test_o3

43

Test_i1

8

ADC_in

9

Bias

7

AVdd1

10

CCD_GND

13

CCD_in

12

FBC

11

SHC

45

SHC

70

AVss12

71

AVss12

46

AVss12

47

AVss12

14

AVss12

17

AVdd2

28

NC

L4203

L4204

L4205

L4202

R4234

0

R4201

100K

R4204

100

R4224

100

R4230

NQR0286-009X

R4227

47

R4231

NQR0286-009X

R4235

0

R4229

NQR0286-009X

R4226

22

R4228

43K

R4223

OPEN

RA4202

100

1

2

3

4

8

7

6

5

RA4203

100

1

2

3

4

8

7

6

5

RA4201

100

1

2

3

4

8

7

6

5

CAM_OUT

CAM_CLK

REG_-7.5V

CCD_OUT

CDSTG_CS

REG_15V

VDIN

TO PARAGON3

HDIN

CDSTG_RST

GND

REG_2.8V

ADIN0

ADIN2

ADIN6

GND

ADIN4

GND

ADIN5

GND

GND

ADIN9

H1

ADIN7

GND

REG_15V

CLKI

CCD_-7.5V

TO MAIN IF

(CN4201)

GND

RG

ADIN3

GND

ADIN11

ADIN1

H2

SUB

GND

V4

V3

V2

REG_15V

ADIN10

V1

ADIN8

TL4213

TL4216

TL4218

TL4217

TL4215

TL4212

TL4205

TL4206

TL4201

TL4202

TL4214

1^/25v

22^

10^

10^

10^

TO CPU

TO PARAGON3

MAIN(CDS/TG) SCHEMATIC DIAGRAM

NOTES: 1. For the destination of each signal and further line connections that are cut off from this diagram, refer to "BOARD INTERCONNECTIONS".

2. The parts with marked ( ) is not used.