Intel® Server Boards SE7320SP2 and SE7525GP2

Functional Architecture

Revision 4.0

27

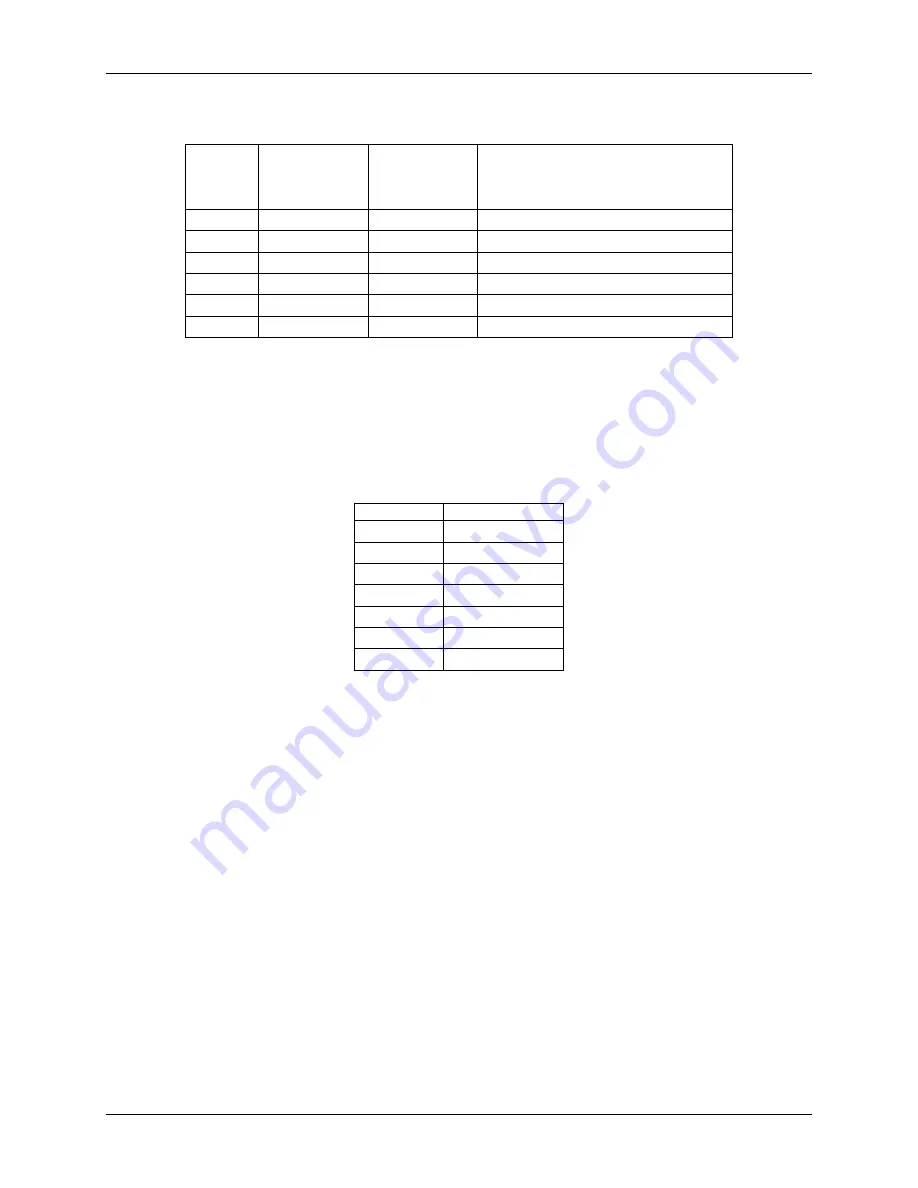

Table 8. Suggested SEC Threashold Prescale Settings

DIMM

Size

SPARECTL

SEC

Prescale

Value

SPARECTL

SEC

Prescale Unit

Thresh_SEC Count on a per DIMM

Basis

128 MB

128

7h = week

4

256 MB

64

7h = week

4

512 MB

32

7h = week

4

1 GB

16

7h = week

4

2 GB

8

7h = week

4

4 GB

4

7h = week

4

In both runtime mode and non-RAS mode, the chipset counter defines the number of CMEs that

can occur on each individual DIMM. The counter for the DIMM is also dependent on the DIMM

size. The table below shows the resulting threshold values based on the DIMM size.

Table 9. DIMM Threshold Values by DIMM Size

DIMM Size

Threshold Value

64 MB

4

128 MB

4

256 MB

4 x 2

512 MB

4 x 4

1 GB

4 x 8

2 GB

4 x 16

4 GB

4 x 32

Example:

If the DIMM in socket 1A 256 MB, its counter value is 08h. If the CME count that occurs on this

DIMM is over 08h, then the DIMM 1A LED will be lit and the CME logging and detection will be

disabled by BIOS.

If the DIMM in socket 2A is 512 MB, its counter value is 10h. If the CME count that occurs on

this DIMM is over 10h, then the DIMM 2A LED will be lit and the CME logging and detection will

be disabled by BIOS.

3.5.5

Memory RASUM Features

The Intel

®

E7320 MCH and Intel E7525 MCH support several memory RASUM (Reliability,

Availability, Serviceability, Usability, and Manageability) features that have traditionally been

found only on high end server systems. These features include x4 SDDC for memory error

detection and correction, Memory Scrubbing, Retry on Correctable Errors, Integrated Memory

Initialization, and DIMM Sparing. The following sections describe how each is supported on

these server boards.

Содержание SE7320SP2 - 800MHZ Ecc Ddr Xeon

Страница 182: ......