Document Number: 002-14826 Rev. *G

Page 57 of 65

PRELIMINARY

CYW43903

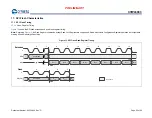

17.1.3 Memory Fast-Read Timing

shows the SPI flash extended and quad memory fast-read timing.

Note:

Regarding

:

1. 24-bit addressing is used, so A[MAX] = A[23] and A[MIN] = A[0].

2. For an extended SPI protocol, C

x

= 7 + (A[MAX] + 1).

3. For a quad SPI protocol, C

x

= 1 + (A[MAX] + 1)/4.

Figure 15. Memory Fast-Read Timing

0

7

8

C

x

MSB

Command

LSB

C

Extended

DQ0

DQ1

High-Z

D

OUT

D

OUT

D

OUT

D

OUT

D

OUT

D

OUT

D

OUT

D

OUT

D

OUT

0

1

2

C

x

C

Quad

DQ[3:0]

MSB

Don’t care

A[MAX]

A[MIN]

LSB

Dummy Cycles

MSB

Command

LSB

A[MAX]

A[MIN]

Dummy Cycles

D

OUT

D

OUT

D

OUT

MSB

LSB