3.6.3 The A/D software trigger register

Writing to this port will perform a software trigger signal to trigger an A/D conversion.

Although the PC can send very fast trigger signal (more than 333 k ), the max. sampling rate of

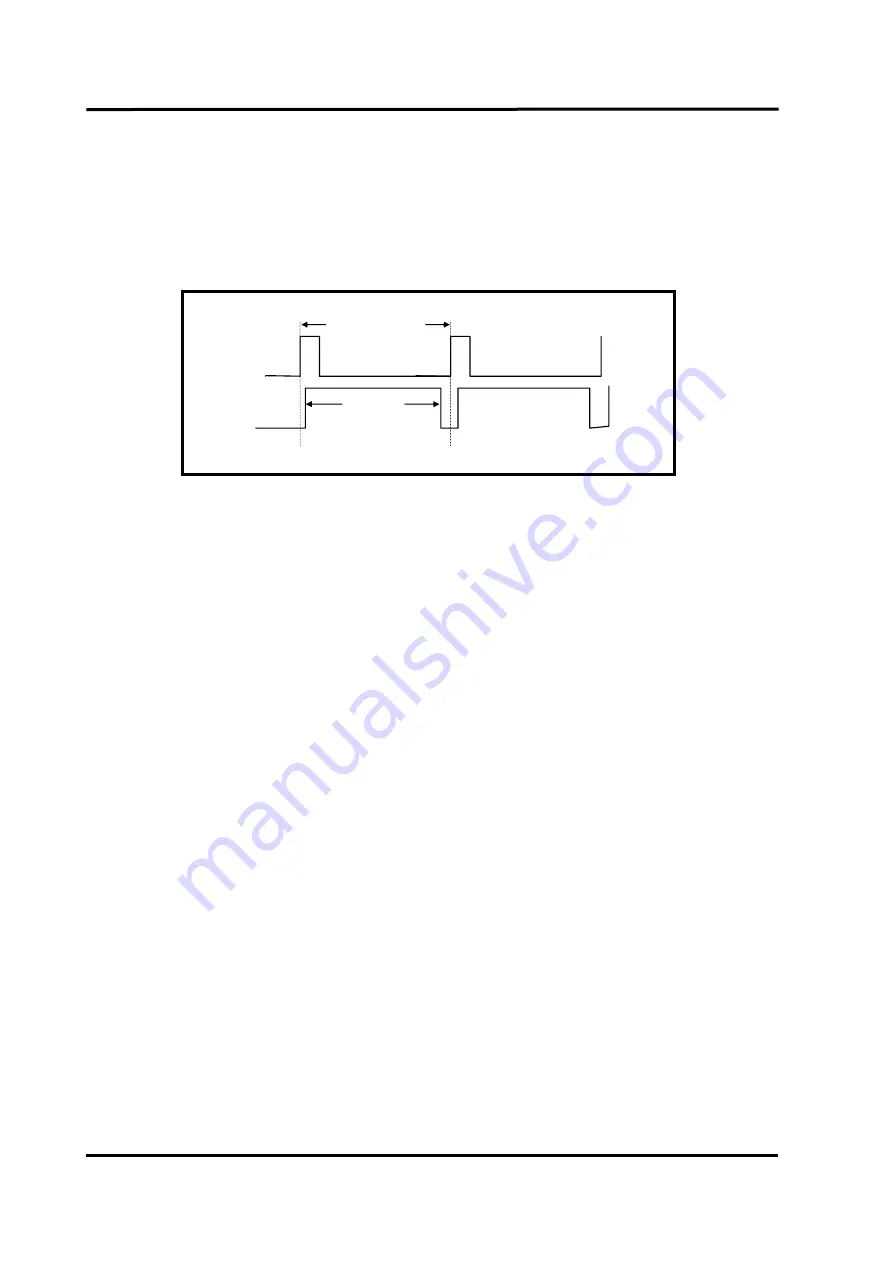

A/D conversion can not over 330 k Samples/Sec.. The timing diagram is given as follows:

Figure 3-3: Trigger delay time.

The demo program of software trigger A/D conversion is given as follows:

WORD P180X_AdPollingHex(Word *AdVal)

{

WORD wVal, wTime;

//Clear FIFO

outport(wAddrCtrl,0x2000); //B15=0=clear FIFO, B13=1=not MagicScan controller cmd

outport(wAddrCtrl,0xA000); //B15=1=no clear FIFO, B13=1= not MagicScan controller cmd

outport((WORD)(wA4),0xffff); /* generate a software trigger pulse */

wTime=0;

for (;;)

{

wVal=inport(wAddrCtrl)&0x20; // wait for ready signal

if (wVal!=0) break;

/* If B4==1

Æ

A/D data ready */

wTime++;

if (wTime>32760) return(AdPollingTimeOut);

}

AdVal=inport(wAddrAdda)&0x0fff; /* Read the available A/D data from FIFO */

return(NoError); /*

0xffff for PCI-1602/1602F

*/

}

z

P1202_AdPollingHex(…) is designed for PCI-1202H/L/HU/LU

z

P1602_AdPollingHex(…) is designed for PCI-1602 and PCI-1602F

A/D

Busy

Software

trigger

3

μ

s

Delay time

Conversion Time

PCI-1202/1602/1800/1802 Hardware User’s Manual

(Ver. 4.2, Dec/2009, PMH-014-42)---- 61