4 - 7

4-4 CPU PORT ALLOCATION (continued)

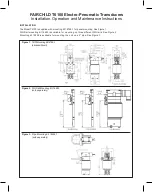

4-5 VOLTAGE BLOCK DIAGRAM

Voltage from the power supply is routed to the whole of the transceiver via regulators and switches.

DC-IN VCC +5V +3CPU

DC

SW

SW

REG

V

3

+

T

Q1000,

D1000, 1001

IC102

Q803−805

Q400−402

IC100

Q800, 801

IC103

Q150−153

D150, 151

T

A

B

Battery pack

T5

N

O

C

P

CHGH CHGC

TXC

VCO UNIT

BCVCOC

VVCOC

UVCOC

AF PWR AMP

(IC400)

AFON

AMBEC

CHG

T5

AF AMP

REG

REG

3.3V

REG

3.2V

REG

+5V

SW

+3V

3.2V

5V

DVC

+5V

REG

+3V

REG

VCO3V

SW

V

5

.

5

+

IC125

DC-DC

PIN

No.

LINE

NAME

DESCRIPTION

IN/

OUT

STATUS

CONDITION

77

RESET

Reset signal from the reset IC (LOGIC UNIT: IC100).

IN

H

–

79

UNLK

Unlock signal from the PLL IC (MAIN UNIT: IC800).

IN

H

PLL is locked.

85

RX232

RS-232 data (RXD).

IN

–

–

86

TX232

RS-232 data (TXD).

OUT

–

–

89

CLSFT

Clock frequency shift signal to the clock oscillator (LOGIC UNIT: X1,

D13).

OUT

H

–

90

PPS

Power save mode control signal to theD PLL IC (MAIN UNIT: IC800).

OUT

L

In power save mode.

91

CHGC

Charging control signal to the charge circuit (LOGIC UNIT: Q150–153,

D150, 151)

OUT

H

While charging.

92

CHGH

Charging current control signal to the charging controller (LOGIC UNIT:

Q150, 152).

OUT

H

Charging current increase.

97

TEMP

The voltage in proportion to the internal temperature.

The voltage divided by R66 (thermistor; LOGIC UNIT) and R67 (LOGIC

UNIT).

IN

–

–

98

RTONE

Weather alert signals.

IN

–

–

96

VIN

DC voltage divided by the voltage detect resisters (LOGIC UNIT: R159

and R160). (Remaining battery capacity detection.)

IN

–

–

99

CTONE

CTCSS signals.

IN

–

–

100

RSSI

RSSI voltage from the IF IC (MAIN UNIT: IC100).

IN

–

–

101

TX-V

• While operated by batteryRSSI voltage from the IF IC (MAIN UNIT:

IC100).

• While perated by external power supplyCurrent in TX from the I-V

converter (MAIN UNIT: IC800).

IN

–

–

102

TTEMP

The voltage in proportion to the TX power AMP (RF UNIT: Q100)

temperature.The voltage divided by R161 (thermistor; RF UNIT) and

R162 (RF UNIT).

IN

–

–

103

CTCOUT

CTCSS/DTCS signals.

OUT

–

–

104

DTMF

Tone (DTMF, european tone: IC-E80D only) signals.

OUT

–

–

109

CPUHV

External power supply detection.

IN

L

E x t e r n a l p o w e r s u p p l y i s

connected.

110

POWER

[POWER] key input. (Pull-up)

IN

L

The key is pushed.

111

D_AS

Analog/Digital mode switching signal.

IN

H

Analog mode.

113

ECK

Clock to the EEPROM (LOGIC UNIT: IC51).

OUT

–

–

114

ESIO

Serial data to the EEPROM (LOGIC UNIT: IC51).

IN/

OUT

–

–

116

CLIN

Key detect signal. (Pushed button is detected by refering input voltage.)

IN

–

–

118

CLOUT

Cloning data.

OUT

–

–