Rev. 1.00

��

��ne 1�� �01�

Rev. 1.00

�5

��ne 1�� �01�

HT46R003B

Cost-Effective A/D 8-bit OTP MCU

HT46R003B

Cost-Effective A/D 8-bit OTP MCU

Watchdog Timer

The Watchdog Timer, also known as the WDT, is provided to prevent program malfunctions or

sequences from jumping to unknown locations, due to certain uncontrollable external events such as

electrical noise.

Watchdog Timer Clock Source

The Watchdog Timer clock source is provided by the LIRC oscillator, the system clock f

SYS

and

its division clock f

SYS

/4, which

are

sourced from the HIRC oscillator. The Watchdog Timer source

clock is then subdivided by a ratio of 2

8

to 2

15

to give longer timeouts, the actual value being chosen

using the WS2~WS0 bits in the WDTS register. The LIRC internal oscillator has an approximate

period frequency of 12kHz at a supply voltage of 5V. However, it should be noted that this specified

internal clock period can vary with V

DD

, temperature and process variations.

Watchdog Timer Control Registers

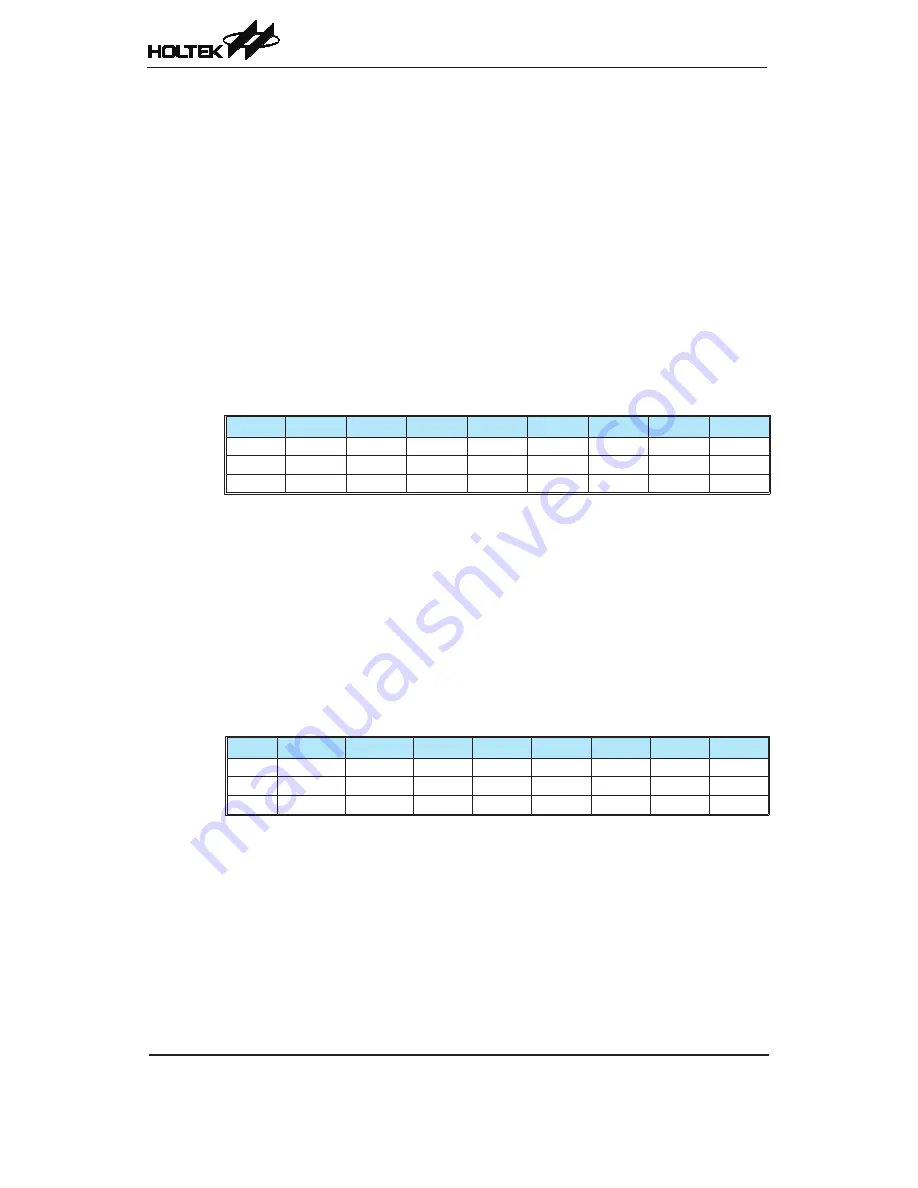

WDTS Register

Bit

7

6

5

4

3

2

1

0

Name

—

—

—

—

—

WS�

WS1

WS0

R/W

—

—

—

—

—

R/W

R/W

R/W

POR

—

—

—

—

—

1

1

1

Bit 7~3

Unimplemented, read as “0”

Bit 2~0

WS2~WS0

: WDT Time-out period selection

000: 2

8

/f

S

001: 2

8

/f

S

010: 2

10

/f

S

011: 2

11

/f

S

100: 2

12

/f

S

101: 2

13

/f

S

110: 2

14

/f

S

111: 2

15

/f

S

These three bits determine the division ratio of the Watchdog Timer source clock,

which in turn determines the timeout period.

WDTC Register

Bit

7

6

5

4

3

2

1

0

Name WDTCLS1 WDTCLS0 WDTEN5 WDTEN� WDTEN3 WDTEN� WDTEN1 WDTEN0

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

POR

0

0

0

0

0

0

0

0

Bit 7~6

WDTCLS1~WDTCLS0

: WDT/Timer/PWM/Time base clock source

00: f

LIRC

01: f

SYS

/4

10: f

SYS

11: f

SYS

Bit 5~0

WDTEN5~WDTEN0

: WDT enable control

000000: Enable

101101: Disable

Other values: MCU reset

When these bits are changed by the environmental noise to reset the microcontroller,

the reset operation will be activated after 2~3 LIRC clock cycles.