Rev. 1.60

186

August 20, 2019

Rev. 1.60

187

August 20, 2019

BS66F340/BS66F350/BS66F360/BS66F370

Touch A/D Flash MCU with LED Driver

BS66F340/BS66F350/BS66F360/BS66F370

Touch A/D Flash MCU with LED Driver

KEY 1

Key

OSC

KEY 2

Key

OSC

KEY 3

Key

OSC

KEY 4

Key

OSC

TKRCOV

Multi-

frequency

MnDFEN

TKMn16DH / TKMn16DL

( to Data Memory Sector 5)

TKCFOV

TK16DL / TK16DH

Mux .

Module 0

TKTMR

Reference Oscillator

TKMnROH / TKMnROL

( from Data Memory Sector 6)

Filter

Module n

16-bit C/F Counter

Filter

f

SYS

/4

M

U

X

MnTSS

TKMnC2

8-bit Time Slot Counter

5-bit unit period counter

8-bit Time Slot Counter

Preload Register

TKTMR

Overflow

16-bit Counter

TK16OV

M

U

X

TK16S1~TK16S0

f

SYS

/4

f

SYS

/2

f

SYS

f

SYS

/8

16-bit C/F Counter

Value

(Sector 5)

Touch Key

Data Memory

Reference Osc.

Capacitor Value

(Sector 6)

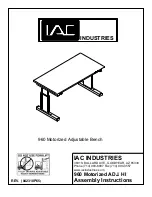

Note: The structure contained in the dash line is identical for each touch key module which contains four touch keys.

Touch Key Function Block Diagram

Touch Key Register Definition

Each touch key module, which contains four touch key functions, has its own suite registers. The

following table shows the register set for each touch key module. The Mn within the register name

refers to the Touch Key module number. The series of devices has up to seven Touch Key Modules

dependent upon the selected device.

Name

Description

TKTMR

Touch key time slot 8-bit counter proload register

TKC0

Touch key function Control register 0

TKC1

Touch key function Control register 1

TK16DL

Touch key function 16-bit counter low byte

TK16DH

Touch key function 16-bit counter high byte

TKMn16DL Touch key module n 16-bit C/F counter low byte

TKMn16DH Touch key module n 16-bit C/F counter high byte

TKMnROL

Touch key module n reference oscillator capacitor select low byte

TKMnROH

Touch key module n reference oscillator capacitor select high byte

TKMnC0

Touch key module n Control register 0

TKMnC1

Touch key module n Control register 1

TKMnC2

Touch key module n Control register 2

Touch Key Module Registers List