HT98R068-1 Two-way Radio OTP MCU

System Clock Switches

In the system setup preliminary stage, the operating frequency controlled by two groups of

registers, CTRL2 [7-5, 3-0] and CTRL0 [0] is firstly selected. The description is as follows:

System Control Register 2 (CTRL2)

Bit

7

6

5

4

3

2

1

0

CTRL2 M1 M0 PLLD2

AUPRST

PLLEN

PLLD1

PLLD0 LXTEN

POR 0 0 1

0

0

1

1

0

CTRL2 [3]: ON/OFF PLL mode 1. This bit controls the PLL on/off. The CTRL2 [7-6] bits

select the PLL ascending frequency which has four system frequencies to meet different

application requirmennts. The CTRL2 [5] bit selects the PLL divider ratio of the audio

processor with one and two times provided. The CTRL2 [2-1] bits is the MCU PLL

divider/multiplier select bits with 1, 2, 4 ratio selections. The CTRL2 [0] bit is LXT low

speed selection bit, which can request the system to enter the IDLE mode when used

together with HALT instruction.

System Control Register 0 (CTRL0)

Bit

7

6

5

4

3

2

1

0

CTRL0 PCFG PFDCS

-

-

- PFDC LXTLP CLKMOD

POR 0 0 - - - 0 0

1

The CTRL0 [0] bit selects the MCU high speed mode. If CTRL0 [0] =1, the MCU operates

in the low speed mode (32,768kHz). If CTRL0 [0] = 0, the MCU operates in the PLL mode.

When using the PLL mode, it is important to note that when the PLL is enabled the PLL

ascending frequency ratio, MCU and audio processor divider ratio must be first selected

after which a delay of 10ms (PLL stabilising time) mus be implemented before allowing it

to be a device clock source. When the MCU is on by using the CTRL0 [0] bit and the

audio processor is turned on by using the CTRL2 [4] bit, the MCU operates in the PLL

mode, it is not recommended that change the PLL divider setting.

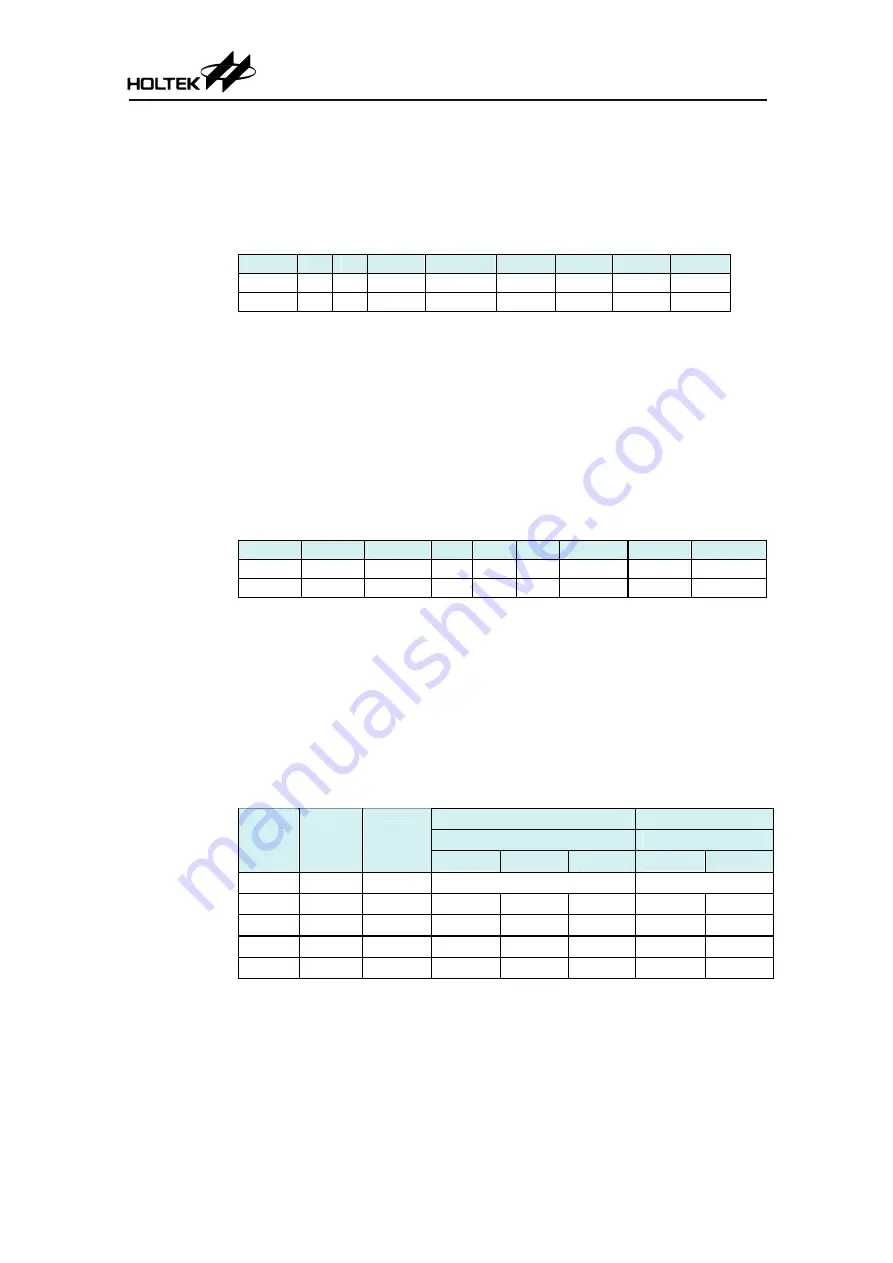

MCU

Audio Processor

PLLD1 , PLLD0

PLLD2

PLLEN

M1,M0

PLL

Speed

0,1 (÷1)

1,0 (÷2)

1,1 (0,0)

0 (÷1)

1 (÷2)

0 X

32.768K

32.768K

32.768K

1 00

8.192M

8.192M

4.096M

2.048M

8.192M 4.096M

1 01

10.24M

10.24M

5.12M

2.56M 10.24M 5.12M

1 10

12.288M

12.288M

6.144M

3.072M

12.288M 6.144M

1 11

16.384M

16.384M

8.192M

4.096M

16.384M 8.192M

X: Don’t care

MCU & Audio Procrssor PLL Divider Table

4