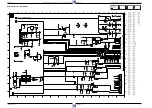

Platinenabbildungen und Schaltpläne / Layout of PCBs and Circuit Diagrams

GDV Modul 1

Platinenabbildungen und Schaltpläne / Layout of PCBs and Circuit Diagrams

GDV Modul 1

23

GRUNDIG Service

24

GRUNDIG Service

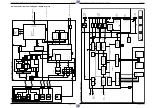

DVD-Monoboard – Prozessor und Decoder / Processor and Decoder

Reference

Oscillograms ..............8

A/V-MUX Board ....4-13

–

1A

......................4-15

–

1B

......................4-17

–

2A

......................4-19

–

2B

......................4-21

Eject Board ...........4-22

DVD-Monoboard ........9

–

1

...........................15

–

2

...........................17

–

3

...........................19

–

4

...........................21

–

5

...........................23

–

6

...........................25

Power Supply.....4-9/11

Seiten "4-…" – siehe Basis-Service-Manual / Pages "4-…" – see Main Service Manual

LPCM

AUDIO

IRQ

PORT 0 I/O

PORT 1 I/O

Subpicture

Video

Audio

SDRAM CONTROLLER

SYSTEM USE

JTAG

PORT 2 I/O

PORT 3 I/O

PORT 4 I/O

FR

ONT

-END

uP ST20cpu

A/V/Sub

demultiplexer

MPEG

DECODER

Subpicture

decoder

TEST

2

I S

ADDRESS

DATA

Interf

ace

MEMORY interface

VIDEO

ENCODER

DECODER

AC3

MPEG1/2

OSC

1501-1 A1

1501-2 B1

1501-3 B1

1501-4 B1

1501-5 B1

2505 B12

2506 D14

2507 D14

2508 E14

2509 E14

2510 I3

3540 C9

3541 B7

2504 C11

3526 F2

2528 I11

2529 I11

1

2

3

4

5

2535 B1

3572 B2

3573 I12

3574 C8

3575 C10

5501 H11

6

7

8

9

10

11

3505 B11

3506 B4

3517 C13

2530 I11

3500 B3

3501 B3

3502 B5

3503 B11

3504 B11

2524 I10

3516 C6

3520 C11

3521 C12

3522 C12

3523 D13

1506-9 B14

2500 A3

2502 B5

2503 B6

1506-7 A14

1506-8 A14

F510 B9

F511 A1

F512 B1

F513 B11

F514 B8

1506-1 A14

1506-10 B14

1506-11 B14

1506-12 B14

1506-13 B14

1506-14 B14

2511 I3

2512 I4

3542 B8

3545 D14

3534 I12

3535 I13

3536 I14

3537 I12

3538 I13

3552 B10

3553 B11

3554 B10

3555 B9

2520 I9

2521 I9

2522 I10

2523 I10

2526 I11

2527 H13

13

14

F542 C9

F543 C7

F544 C9

F545 C9

F546 C9

5502 I11

5503 A1

5504 B1

7501 B5

7503 D2

7504 I13

12

13

3507 B5

3508 B11

2531 I11

2532 B1

2533 A1

2534 B1

3524 D14

3525 E14

3515 C6

1506-21 C14

1506-22 C14

1506-23 D14

1506-24 D14

1506-3 A14

3519 C9

1506-5 A14

1506-6 A14

H

I

F578 G2

F579 G2

F580 G2

F581 G2

F582 G2

F515 B1

F516 B1

F517 B11

F518 B6

F519 C9

F520 C7

1506-15 B14

1506-16 C14

2513 I4

2514 I4

3546 C7

3547 B6

3548 A10

3549 B10

3550 B10

3551 B10

2519 I9

5

6

7

8

9

2525 I10

11

12

3570 F14

3571 A2

F539 C9

F540 C6

F541 C12

F574 G14

F576 G14

F547 C9

F548 C9

F549 C9

F552 C7

F553 C8

F554 D8

7505 A2

F050 I14

14

A

3509 B11

3511 C6

3512 C6

3513 A10

T

O

/FR

OM DISPLA

Y

3514 C6

1506-20 C14

I

A

B

C

D

1506-4 A14

F

G

F508 B9

F509 B9

F586 H11

F587 H13

F588 H12

F589 H12

F590 H13

F592 I8

F593 I8

F594 I8

F595 I8

F596 I8

F597 I8

F521 C10

F522 C11

1506-17 C14

1506-18 C14

2515 I4

2516 I5

2517 I5

2518 I5

I2C Bus

SYSTEM ADDRESS Bus

4

3561 B9

3562 C7

3563 C7

3564 C7

3565 C8

10

3567 C7

3568 C8

F537 C11

F538 C6

F527 C7

F528 C11

F529 D7

F530 C10

F531 C10

F555 D6

F556 D12

F557 D12

F558 D14

F559 E14

F560 E14

F055 D14

F056 F14

F051 I14

F052 C7

B

C

D

E

SDRAM Interface

SYSTEM DATA Bus

H

F500 A13

F501 A11

F502 B5

F503 A6

F504 B9

E

F506 B9

F507 B9

F583 G2

F585 H11

F567 F14

F568 F2

F569 F14

F573 G14

F505 B9

F058 C7

F059 C8

F523 C13

F524 C10

F525 C11

F526 C7

3556 B9

3557 B9

3558 B9

3559 B9

1506-19 C14

1506-2 A14

1

2

BASIC ENGINE INTERFACE Bus

3

3560 B9

F532 C10

F533 C10

F534 C10

F535 C5

F536 C6

3566 C7

F562 E14

F564 F14

F598 I8

F599 I8

OPTION

OPTION

OPTION

OPTION

OPTION

OPTION

OPTION

OPTION

OPTION

OPTION

OPTION

OPTION

F053 C7

F054 C12

RAM/ROM Interface

HSYNC

F

G

F060 C8

F566 F14

F500

F581

1506-21

21

3568

F558

100n

2515

10K

3526

2530

4u7

10K

3506

2505

22n

F540

2500

100n

2u2

1506-13

13

5502

100p

VDD_STI

F539

2504

1501-2

3511

3K3

1506-18

18

F556

3514

10K

100R

3550

F587

100n

2514

F501

3505

10K

F574

10K

3504

F557

3549

F535

VDD_STI

F522

3552

3553

F506

F530

100R

3513

10K

VDD_STI

F566

3K3

3500

3555

2u2

5501

F523

F529

3559

3K3

3501

F576

F583

F578

2525

F527

100n

2518

100n

3565

F579

2532

47p

F562

F533

F559

VDD_STI

100n

2503

330R

3537

1506-24

24

F580

1506-14

14

VDD_STI

F518

3536

100R

F589

F596

F532

3K3

3517

VDD_STI

22

3540

4K7

100n

2510

1506-22

100n

2513

23

1506-11

11

3K3

3512

1506-23

3524

100R

F505

VDD_STI

3558

3522

10K

F513

3554

100n

F548

1506-15

15

2519

F585

F059

2535

1n

F520

1501-4

1

VDD_STI

1n

2534

VSSA1

54

VSSA2

61

VSSA_PCM

50

V_REF_D

A

C_RGB

58

V_REF_D

A

C_YCC

65

WE0n

121

WE1n

122

Y_OUT

62

1506-1

171

VDD16

184

VDD17

208

VDD2

18

VDD3

34

VDD4

67

VDD5

75

VDD6

86

VDD7

95

VDD8

102

VDD9

110

VDD

A1

53

VDD

A2

60

VDDA_PCM

48

VREF_PCM

49

TDI

186

TDO

189

TEST1

30

TEST2

31

32

TEST3

TEST4

33

TEST5

41

TMS

187

TRSTn

190

VDD1

1

VDD10

119

VDD11

130

VDD12

139

VDD13

149

VDD14

159

VDD15

PPC_CLK

137

PPCn_MODE

138

RAS0n_OR_CE4n

127

RAS1n_OR_HOLDREQ

128

136

READ

Y

RSTn

29

R_OUT

57

133

R|W_|DMAACK

SCLK

43

SDCASn

89

SDCS0n

84

SDCS1n

85

SDRASn

88

SD

WEn

90

SPDIF_OUT

47

TCK

188

202

PIO-3|2

203

PIO-3|3

204

PIO-3|4

205

PIO-3|5

206

PIO-3|6

207

2

PIO-3|7

PIO-4|0

191

PIO-4|1

192

PIO-4|2

193

PIO-4|3

194

PIO-4|4

195

PIO-4|5

196

PIO-4|6

197

PIO-4|7

14

PIXCLK_27MHz

118

17

PIO-0|5

20

PIO-0|7

22

PIO-1|0

9

PIO-1|2

10

PIO-1|3

198

199

PIO-1|4

PIO-1|5

11

PIO-1|6

12

PIO-1|7

13

PIO-2|0

3

PIO-2|3

5

PIO-2|4

6

PIO-2|5

7

PIO-2|7

8

PIO-3|0

201

PIO-3|1

25

I_REF_D

A

C_RGB

59

I_REF_D

A

C_YCC

66

LRCLK

46

MEMCLKIN

104

MEMCLK

OUT

76

ODD_OR_EVEN

52

OEn

123

OSD_A

CTIVE

117

24

PCM-OUT1

21

PCM-OUT2|PIO-0|6

PCM_CLK

45

PCM_OUTO

44

PIO-0|0

15

PIO-0|3

16

PIO-0|4

150

GND14

160

GND15

172

GND16

185

GND17

200

GND2

19

GND3

35

GND4

68

GND5

77

GND6

87

GND7

96

103

GND8

GND9

111

G_OUT

56

HSYNCn

51

IRQ0

2

3

IRQ1

DQ15

115

DQ2

94

DQ3

97

DQ4

98

DQ5

99

DQ6

100

DQ7

101

DQ8

106

DQ9

107

DQML

91

DQMU

105

GND1

4

GND10

120

GND11

131

GND12

140

GND13

DATA2

143

DATA3

144

DATA4

145

DATA5

146

DATA6

147

DATA7

148

DA

T

A

8

151

DA

T

A

9

152

DMAXFER

134

DQ0

92

DQ1

93

DQ10

108

DQ11

109

DQ12

112

DQ13

113

DQ14

114

CAS1n_OR_DMAREQn

132

CE1n

124

CE2n

125

CE3n

126

CSn

135

CVBS_OUT

64

C_OUT

63

DATA0

141

DATA1

142

DA

T

A

1

0

153

DA

T

A

1

1

154

DA

T

A

1

2

155

DA

T

A

1

3

156

DA

T

A

1

4

157

DA

T

A

1

5

158

ADR6

166

ADR7

167

ADR8

168

ADR9

169

A

UXCLK

116

BRM0_OR_OSLINK_SEL

26

BRM1_OR_BOO

TFR

OMR

OM

27

BRM2

28

B_BCLK

37

B_DATA

36

B_FLAG

38

B_OUT

55

B_SYNC

39

B_V4

42

B_WCLK

40

CAS0n_OR_HOLDACK

129

ADR10

170

ADR11

173

ADR12

174

ADR13

175

ADR14

176

ADR15

177

ADR16

178

ADR17

179

ADR18

180

ADR19

181

ADR2

162

ADR20

182

ADR21

183

ADR3

163

ADR4

164

ADR5

165

STI5505

AD0

78

AD1

79

AD10

82

AD11

83

AD2

80

AD3

81

AD4

69

AD5

70

AD6

71

AD7

72

AD8

73

AD9

74

ADR1

161

F582

7503

2531

4u7

F536

100n

2523

F538

F567

100n

2521

F564

4

+5Vstby

3561

1506-4

1506-10

10

100n

2516

VDD_STI

F586

F552

2509

330p

3564

VDD_STI

F516

VDD_STI

F517

F560

F515

F593

F526

1506-3

3

F545

10K

3516

3556

VDD_STI

VDD_STI

VDD_STI

1501-5

9

3509

10K

F050

1506-9

VDD_STI

1506-16

16

1506-17

17

F509

F507

2526 100n

3515 10K

F051

F590

F058

3560

F056

3567

3538

680R

VDD_STI

VDD_STI

10K

3519

1506-19

19

3502

22K

F055

F053

1506-5

5

3545

220R

1506-6

6

3K3

3523

2502

4u7

F541

2522 100n

F549

F525

+5Vstby

M24C32

7505

1

E0

2

E1

3

E2

6

SCL

5

SDA

8

VCC

4

VSS

7

WC_

VDD_STI

100n

2517

F054

2512 100n

100n

2507

F546

1

VDD

4

1506-2

2

7504

FXO-31FT

GND

2

OUT

3

TS

2527

1501-3

F052

100n

47p

2533

F543

3535

15K

F598

F588

F534

3575

3548

F547

3n3

2508

F537

F555

2524 100n

3521

10K

10u

F511

BC847B

2506

100R

3573

7501

3525

F568

10K

VDD_STI

VDD_STI

F060

3547

3K3

F597

68R

3572

3562

3563

F595

VDD_STI

F528

100n

2520

5503

F594

F542

+5VOSC

3566

F503

VDD_STI

VDD_STI

VDD_STI

VDD_STI

1506-8

8

F569

100n

2528

F514

3574

F502

F524

F544

F504

VDD_STI

3520

10K

F510

1506-12

12

3503

10K

F519

F508

100n

2529

5504

VDD_STI

F573

20

VDD_STI

3534

10K

1506-20

3570

100R

3557

1501-1

3551

F592

68R

3571

100R

VDD_STI

F512

7

VDD_STI

3541

47R

3542

47R

1506-7

4K7

3507

3508

68R

100n

2511

VDD_STI

3546

100R

F521

F553

F531

F554

F599

+5Vstby

SDA_EXE

OSD_A

CTIVE

SEL_A

CLK2

SEL_A

CLK1

RESET_I2C

SEL_A

CLK1

27M_CLK

27M_CLK

27M_CLK

SER

VICE

SER

VICE

RESETN

TCK

PCMout1

PCMout2

SD

A

P50

STB_CONT

PCM_CLK

CE1

centre_on

kar_b

y_pass

SPDIF_OUT

SCL_EXE

{SCLK

o

,PCM_OUT

O

,PCM_CLK,LRCLK

o

,SPDIF_OUT

,R_OUT

,G_OUT

,B_OUT

,C_OUT

,CVBS_OUT

,Y_OUT

,27M_CLK}

WAIT

A

UXCLK

B_SYNC

B_V4

B_BCLK

B_FLAG

YC5

YC4

YC3

YC2

YC1

YC0

IRQ_I2C

27M_CLKOUT

YC0

YC1

YC2

YC3

YC4

YC5

YC6

YC7

OSD_ACTIVE

VSYNC

VSYNC

HSYNC

TXD_SER

CPUanalyse

ErrorOUT

FLASH_OEN

YC7

centre_on

kar_b

y_pass

MUTE

RXD_SER

YC6

HSYNC

FLASH_OEN

OSLINKIN

AD6

AD5

AD4

AD3

AD2

AD1

AD0

SCL

SDA

CTS_SER

R

TS_SER

B_DATA

B_WCLK

OSLINK

O

UT

CPUreset

CASN

CSN2

CSN1

DQ15

DQ14

DQ13

DQ12

DQ11

DQ10

DQ9

DQ8

DQ7

DQ6

DQ5

DQ4

DQ3

DQ2

DQ1

DQ0

AD11

AD10

AD9

AD8

AD7

D8

D9

D10

D11

D12

D13

D14

D15

TDO

LRCLKo

PCM_OUTO

SCLKo

G_OUT

B_OUT

DQMU

DQML

WEN

RASN

RAS0ND

RAS1ND

RWN

A20

A19

A18

A17

A16

A15

A14

A13

A12

A11

A10

A9

A8

A7

A6

A5

A4

A3

A2

A1

CAS1ND

CE_ROMN

D0

D1

D2

D3

D4

D5

D6

D7

CLK

OEND

SCL

TXD_BE

RXD_BE

RSTN

STB_CONT

CVBS_OUT

C_OUT

Y_OUT

R_OUT

TMS

TDI

TRSTN

OS_BOO

T

CAS0ND

041000