86

CHAPTER 7 DETAILED EXECUTION INSTRUCTIONS

7.15

AND (And Word Data of Source Register to Data in

Memory)

Takes the logical AND of the word data at memory address "Ri" and the word data in

"Rj", stores the results to the memory address corresponding to "Ri".

The CPU will not accept hold requests between the memory read operation and the

memory write operation of this request.

■

AND (And Word Data of Source Register to Data in Memory)

Assembler format:

AND Rj, @Ri

Operation:

(Ri) and Rj

→

(Ri)

Flag change:

N:

Set when the MSB of the operation result is "1", cleared when the MSB is "0".

Z:

Set when the operation result is "0", cleared otherwise.

V and C: Unchanged

Execution cycles:

1 + 2a cycles

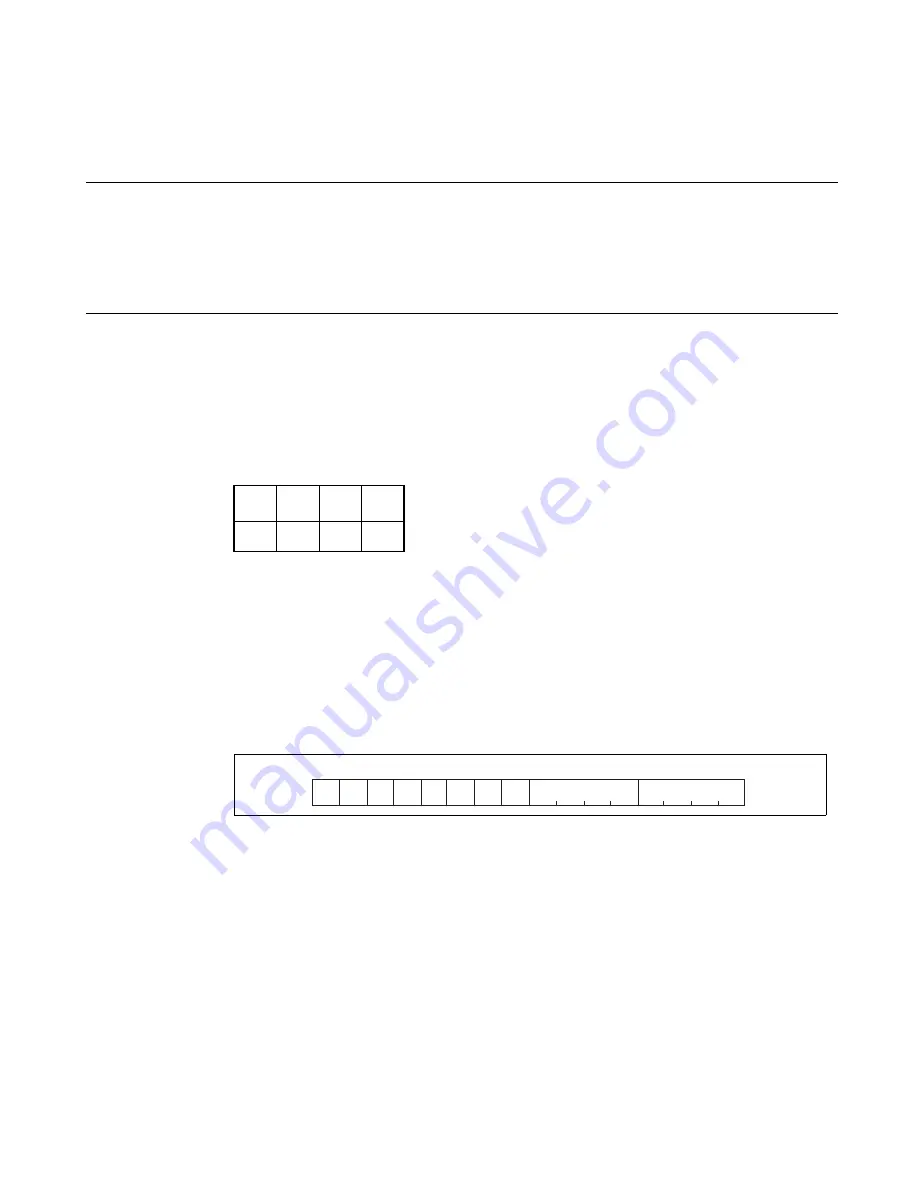

Instruction format:

N

Z

V

C

C

C

–

–

MSB

LSB

1

0

0

0

0

1

0

0

Rj

Ri

Содержание FR Family

Страница 2: ......

Страница 3: ...FUJITSU LIMITED FR Family 32 BIT MICROCONTROLLER INSTRUCTION MANUAL ...

Страница 4: ......

Страница 8: ...iv ...

Страница 14: ...x ...

Страница 36: ...12 CHAPTER 2 MEMORY ARCHITECTURE ...

Страница 284: ...260 CHAPTER 7 DETAILED EXECUTION INSTRUCTIONS ...

Страница 301: ...277 INDEX INDEX The index follows on the next page This is listed in alphabetical order ...

Страница 314: ......