Chapter 4

Signal Connections

©

National Instruments Corporation

4-29

PCI-MIO E Series User Manual

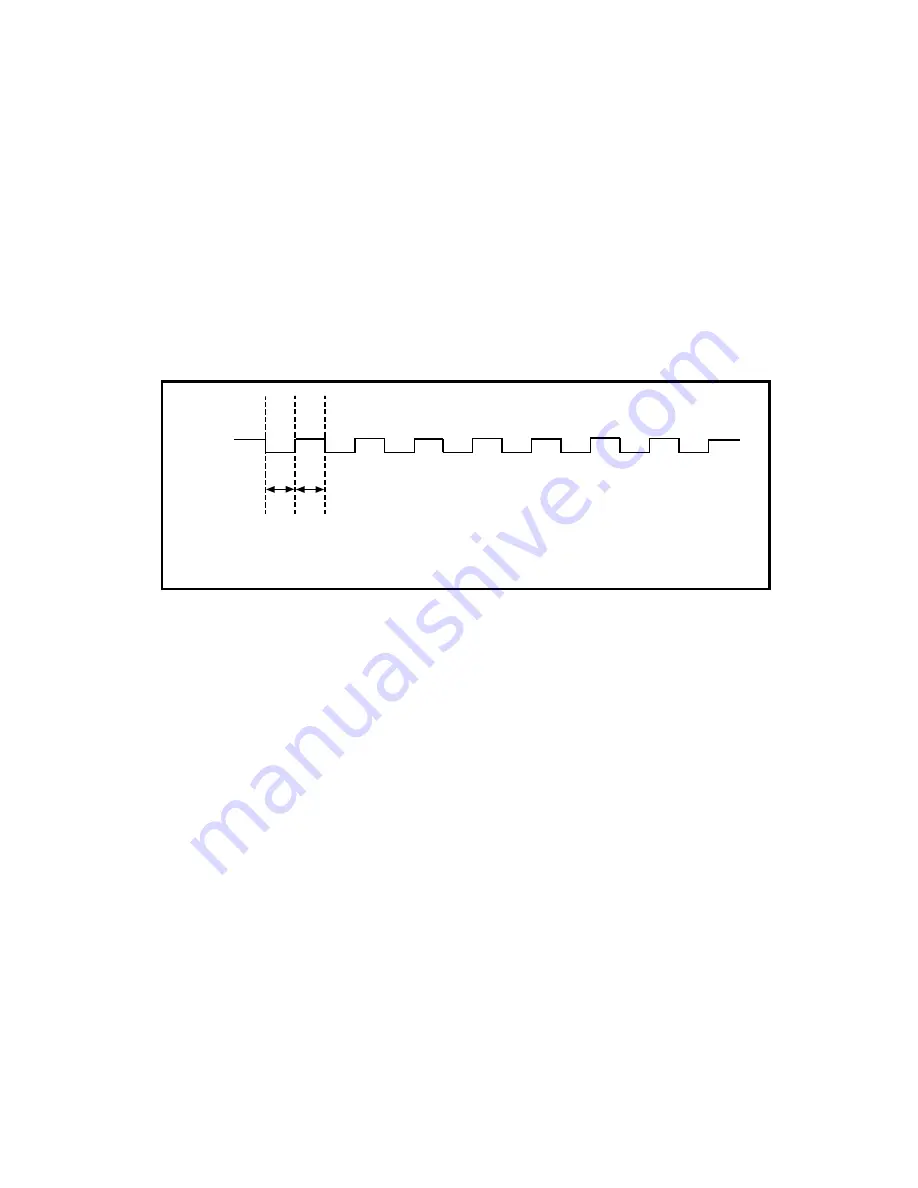

EXTSTROBE* Signal

EXTSTROBE* is an output-only signal that generates either a single

pulse or a sequence of eight pulses in the hardware-strobe mode. An

external device can use this signal to latch signals or to trigger events.

In the single-pulse mode, software controls the level of the

EXTSTROBE* signal. A 10

µ

s and a 1.2

µ

s clock are available for

generating a sequence of eight pulses in the hardware-strobe mode.

Figure 4-14 shows the timing for the hardware-strobe mode

EXTSTROBE* signal.

Figure 4-14. EXTSTROBE* Signal Timing

TRIG1 Signal

Any PFI pin can externally input the TRIG1 signal, which is available

as an output on the PFI0/TRIG1 pin.

Refer to Figures 4-11 and 4-12 for the relationship of TRIG1 to the

DAQ sequence.

As an input, the TRIG1 signal is configured in the edge-detection mode.

You can select any PFI pin as the source for TRIG1 and configure the

polarity selection for either rising or falling edge. The selected edge of

the TRIG1 signal starts the data acquisition sequence for both

posttriggered and pretriggered acquisitions. The PCI-MIO-16E-1,

PCI-MIO-16E-4, and PCI-MIO-16XE-10 support analog triggering on

the PFI0/TRIG1 pin. See Chapter 3, Hardware Overview, for more

information on analog triggering.

t w t w

VOH

VOL

t w = 600 ns or 5

µ

s