DS21354 & DS21554

96 of 117

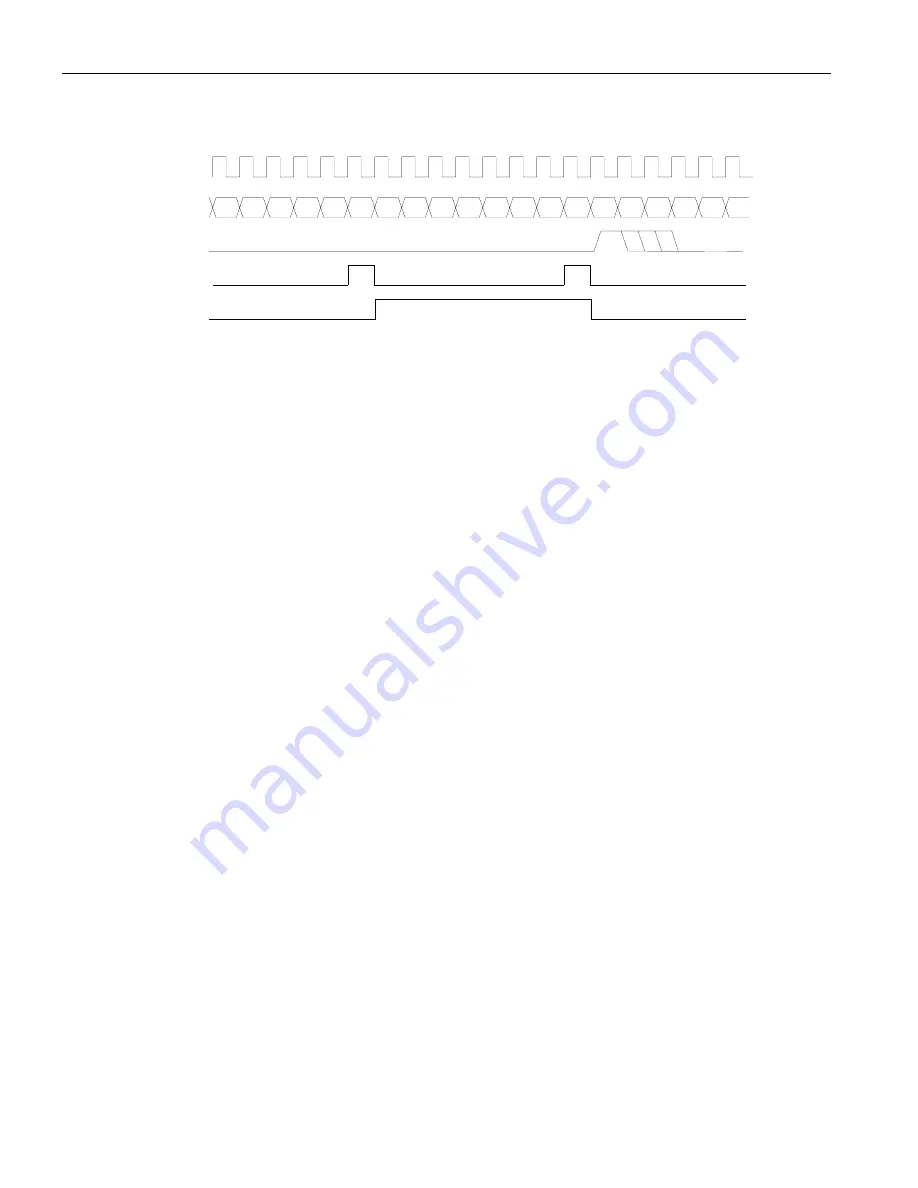

TRANSMIT SIDE 1.544 MHz BOUNDARY TIMING

(with elastic store enabled)

Figure 19-9

Notes:

1. The F bit position in the TSER data is ignored

2. TCHBLK is programmed to block channel 24

LSB

F

MSB

LSB MSB

CHANNEL 1

CHANNEL 24

TSYSCLK

TSER

TSSYNC

TCHCLK

TCHBLK

CHANNEL 23

1

2