KAD/ADC/129/S2

8

Bias current return path

As shown in Figure 4 on page 7, the analog inputs can be used as differential inputs (that is, not from a bridge). In this case, if

the signal source is isolated with respect to the Acra KAM-500 (for example a battery), a common-mode resistance between the

negative input and ground (GND) should be used to provide a return for bias currents and reduce common-mode noise pick-up.

Because the bias currents are in the order of nAs resistors up to 10k

Ω

can be used. In most cases a short (0Ω) is recommended.

N

OTE

:

When analog inputs are used as differential inputs, setting the excitation and balance to zero reduces quiescent currents

of the module.

Using high primary gains

For gains above 1000, the gain-bandwidth product of the amplifier reduces the bandwidth of the instrumentation amplifier to

approximately 60kHz. The effect of attenuation can be seen for input signals with frequencies of 10kHz and higher.

Excitation setup

Excitation can contribute error to the overall measurement, so it is recommended to use as close as possible to full-scale

excitation, to minimize the percentage error.

For optimal accuracy ensure each channel uses its corresponding excitation. If the excitation is not used, it should be set to the

minimum value.

Excitation drift on potentiometer configurations

Curtiss-Wright recommends a full-bridge input configuration for the KAD/ADC/129/S2. With this configuration the differential

input amplifier removes common mode voltage or common mode pickup noise on the input lines.

For potentiometer circuits where the negative input is tied to ground, excitation drift can have a direct impact on the input signal

either as a gain or an offset error. Note that excitation can drift up to 0.3% on an FSR of 5.1V. In the case where both excitation

lines drift in the same direction an offset error is seen in the measurement. The worst case possible offset is 0.3% of 5.1V and

results in a worst case 15.3mV offset of the measurement. This does not happen with full-bridge configurations. We recommend

that the negative input is tied to ground as shown in Figure 3 on page 7. If the negative input is floating, the drift of the

digital/analog converter related to the balancing input directly adds further offset error to the measurement.

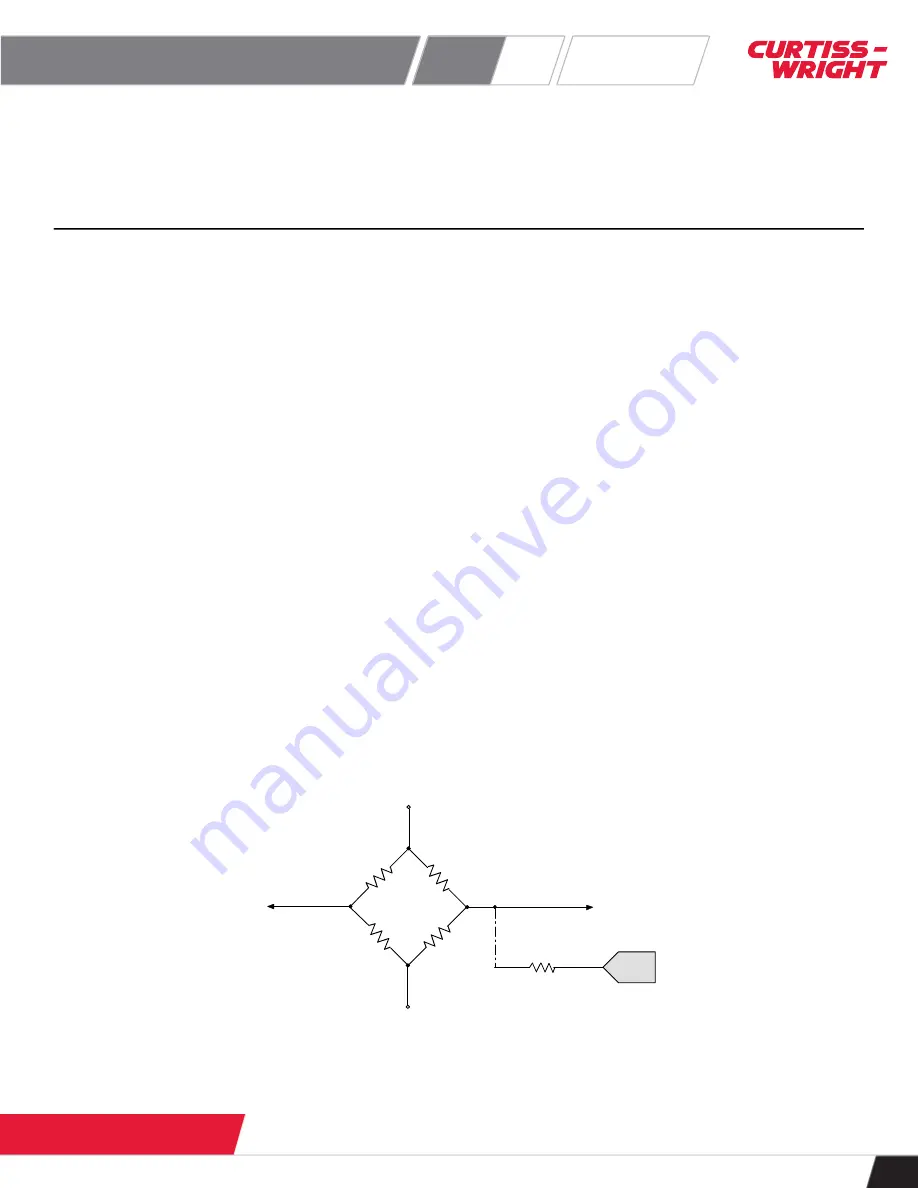

Source load error caused by the balance adjust circuit

The balance circuit has an impedance of R

ADJ

and is connected to the ANALOG(x)- input of the module. This connection is

performed internally on the module. In some bridge configurations, R

ADJ

loads the source signal causing a quantifiable error. An

example schematic for a full-bridge configuration loaded with balance resistance is shown in the following figure.

Figure 5: Full-bridge configuration loaded with balance resistance

EXC_V(x)+

DIGITAL

ANALOG

34.8 K

R1

R2

R3

R4

To Inst Amp In-

V-

Vadj

V+

Rp = R2 // R4

Radj

EXC_V(x)-

(*)

Connection betw een V- and Radj is internal or external depending on module

(*)

ANALOG(x) -

To Inst Amp In+

ANALOG(x)+