12

Avago Technologies Confidential

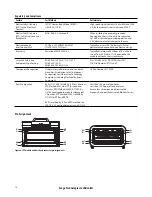

Pin

Signal Name

Signal Description

Logic

Notes

A1

GND

Ground

A2

TX1p

Transmitter Non-Inverted Data Input

CML-I

A3

TX1n

Transmitter Inverted Data Input

CML-I

A4

GND

Ground

A5

TX3p

Transmitter Non-Inverted Data Input

CML-I

A6

TX3n

Transmitter Inverted Data Input

CML-I

A7

GND

Ground

A8

TX5p

Transmitter Non-Inverted Data Input

CML-I

A9

TX5n

Transmitter Inverted Data Input

CML-I

A10

GND

Ground

A11

TX7p

Transmitter Non-Inverted Data Input

CML-I

A12

TX7n

Transmitter Inverted Data Input

CML-I

A13

GND

Ground

A14

TX9p

Transmitter Non-Inverted Data Input

CML-I

A15

TX9n

Transmitter Inverted Data Input

CML-I

A16

GND

Ground

A17

TX11p

Transmitter Non-Inverted Data Input

CML-I

A18

TX11n

Transmitter Inverted Data Input

CML-I

A19

GND

Ground

A20

SCL

Two-wire serial interface clock

LVCMOS-I/O

1

A21

SDA

Two-wire serial interface data

LVCMOS-I/O

1

B1

GND

Ground

B2

TX0p

Transmitter Non-Inverted Data Input

CML-I

B3

TX0n

Transmitter Inverted Data Input

CML-I

B4

GND

Ground

B5

TX2p

Transmitter Non-Inverted Data Input

CML-I

B6

TX2n

Transmitter Inverted Data Input

CML-I

B7

GND

Ground

B8

TX4p

Transmitter Non-Inverted Data Input

CML-I

B9

TX4n

Transmitter Inverted Data Input

CML-I

B10

GND

Ground

B11

TX6p

Transmitter Non-Inverted Data Input

CML-I

B12

TX6n

Transmitter Inverted Data Input

CML-I

B13

GND

Ground

B14

TX8p

Transmitter Non-Inverted Data Input

CML-I

B15

TX8n

Transmitter Inverted Data Input

CML-I

B16

GND

Ground

B17

TX10p

Transmitter Non-Inverted Data Input

CML-I

B18

TX10n

Transmitter Inverted Data Input

CML-I

B19

GND

Ground

B20

VCC3.3-TX

+3.3 V Power supply Transmitter

B21

Not used

Not used , 3.3 V only

Note:

1. Host shall use a pull up of 1.5 kohm – 10 kohm to Vcc3.3.