AT90S4414/8515

13

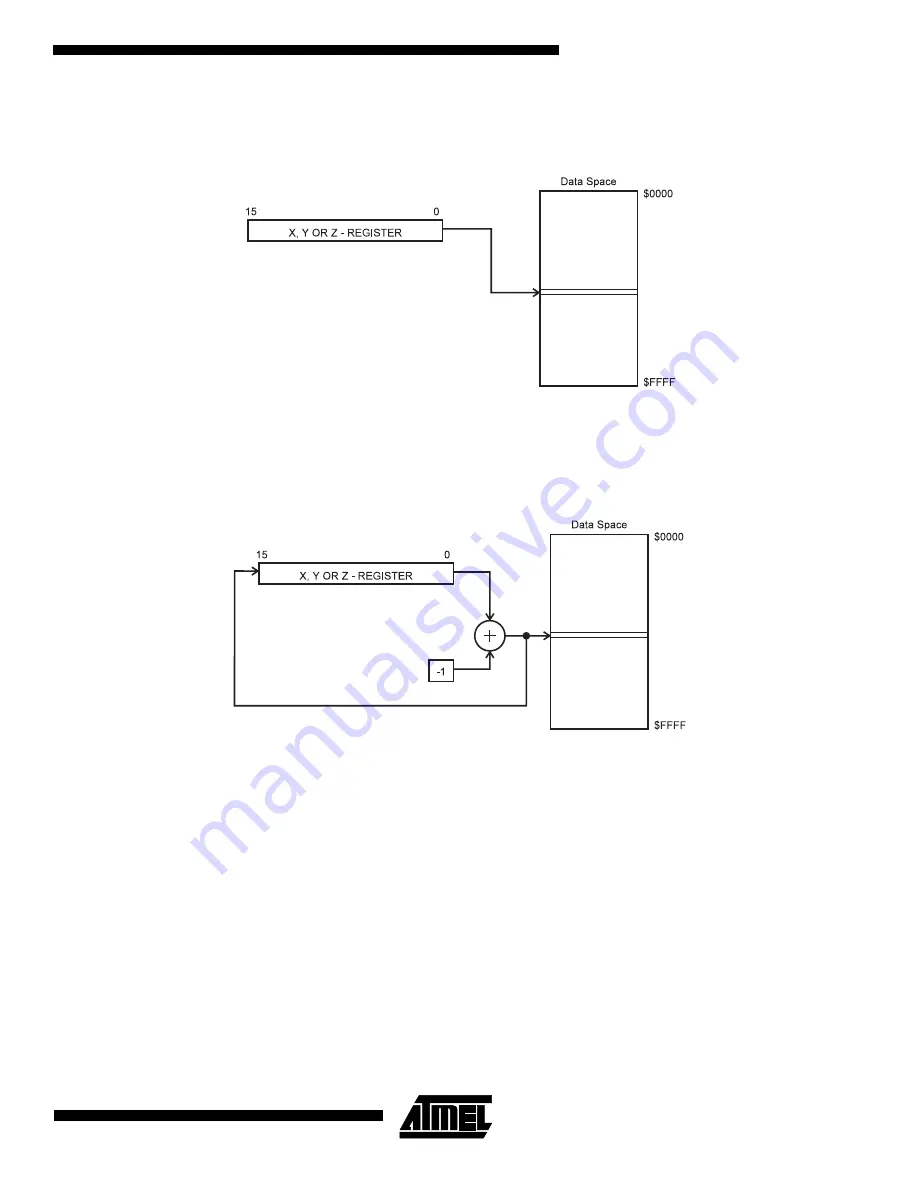

Data Indirect

Figure 14. Data Indirect Addressing

Operand address is the contents of the X, Y or the Z-register.

Data Indirect with Pre-decrement

Figure 15. Data Indirect Addressing with Pre-decrement

The X, Y or the Z-register is decremented before the operation. Operand address is the decremented contents of the X, Y

or the Z-register.