UG-580

EVAL-SSM3515Z User Guide

Rev. A | Page 4 of 19

SETTING UP THE HARDWARE

POWER SUPPLY CONFIGURATION

The PVDD and GND binding posts are used to power the

board. Take care to connect the dc power with correct polarity

and voltage. Reverse polarity or overvoltage can damage the

board permanently. The supply voltages range is from 4.5 V to

17 V; higher voltages can damage the amplifier. Alternately, the

P3 2-pin, 0.1 inch header can be used to connect the external

supply. When inserted, JP2 turns on the power-on LED.

U1 is a 3.3 V regulator included to power up the on-board SPDIF

receiver. JP1 provides the input to the 3.3 V regulator. If the on-

board SPDIF receiver is used, JP1 must be inserted.

The U2 regulator is included as an option to provide the 1.8 V

(DVDD) power to the

and other on-board supporting

circuits. Alternately, the external 1.8 V source can be connected

via the IOVDD binding post. Use P1 to select the external vs.

internal 1.8 V source.

REGULATOR ENABLE

In addition to the 4.5 V to 17 V power supply, a voltage must

be present to activate the integrated voltage regulators on the

amplifier has an internal regulator

to provide a clean internal 5 V (AVDD) rail, as well as an

internally generated 1.8 V (DVDD) rail.

When the REGEN pin is pulled high, by connecting the top two

pins of J9 (REG_EN to PVDD), the internal DVDD regulator is

enabled. If the REGEN pin is pulled low, the regulators are disabled

and the 1.8 V DVDD must be present for the

to function.

DIGITAL AUDIO INPUT

M1 and J1 on the evaluation board provide the SPDIF optical or

coaxial input connectors. The S1 switch selects the desired

source. The U3 IC receives the SPDIF signal and generates the

serial digital output suitable for the

. The default

format is set as I

2

S, 2-channel with 32 bits/channel. The serial

outputs are level shifted to 1.8 V using U6, U7, and U8 before

feeding to the

. Alternatively, a suitable I

2

S/TDM-

compatible source such as a DSP serial port or Audio Precision

digital serial port can be connected at P2. The P12 header

selects either the SPDIF or external source.

INPUT CONFIGURATION

There are several ways to source audio to the

on the

evaluation board. The evaluation board can accept direct

I

2

S/TDM data or it can convert from 2-channel SPDIF/optical

digital audio data to I

2

S using an on-board digital audio receiver

(CS8416-CZZ).

To make a connection from either the on-board audio receiver

circuitry or the P2 external digital audio header to the

device pins, jumpers must be inserted across all three rows of

H2. In some use cases, such as high speed clocking of data,

remove the jumpers across H2 to reduce stub length and

minimize parasitics. In this case, source digital audio data on

the H1 header block.

When using an I

2

S or TDM source, such as from Audio Precision,

it is recommended to source the input audio signals directly to

the FSYNC, BCLK, and SDATAI pins of the P2 header block.

When connecting multiple

evaluation boards on the

same digital audio bus in a daisy-chain configuration, note that

the P5 header port has the same direct connections to the

To route the externally sourced I

2

S or TDM data to the

pins, insert jumpers across SDATAI_EXT, FSYNC_EXT, and

BCLK_EXT on the P12 header block.

If the user does not have a direct I

2

S or TDM source, the on-

board digital audio receiver can accept SPDIF data from a

digital audio source, such as the digital audio output of a

compact disk player. In this case, select either optical or SPDIF

on the S1 switch to properly connect the desired input to the

digital audio receiver.

To route the on-board converted SPDIF-to-I

2

S data to the

pins, insert jumpers across SDATAI_INT, FSYNC_INT,

and BCLK_INT on the P12 header block. Note that the audio

performance is limited to that of the on-board digital audio

receiver (CS8416-CZZ).

I

2

C CONTROL PORT

The

supports I

2

C control with the state of the ADDR pin

(J11 and J4) determining the I

2

C device address. Inserting a

jumper across J4 shorts across a 47 kΩ resistor. Removing the

jumper across J4 inserts the resistor in the signal path for pull-

up or pull-down operation. A jumper inserted across the top

two pins of J11 pulls the ADDR pin to a high state (IOVDD),

whereas inserting a jumper across the bottom two pins of J11

pulls the ADDR pin to a low state (GND). To set the ADDR pin

to open condition, insert a jumper across J4 and do not insert

jumpers on J11.

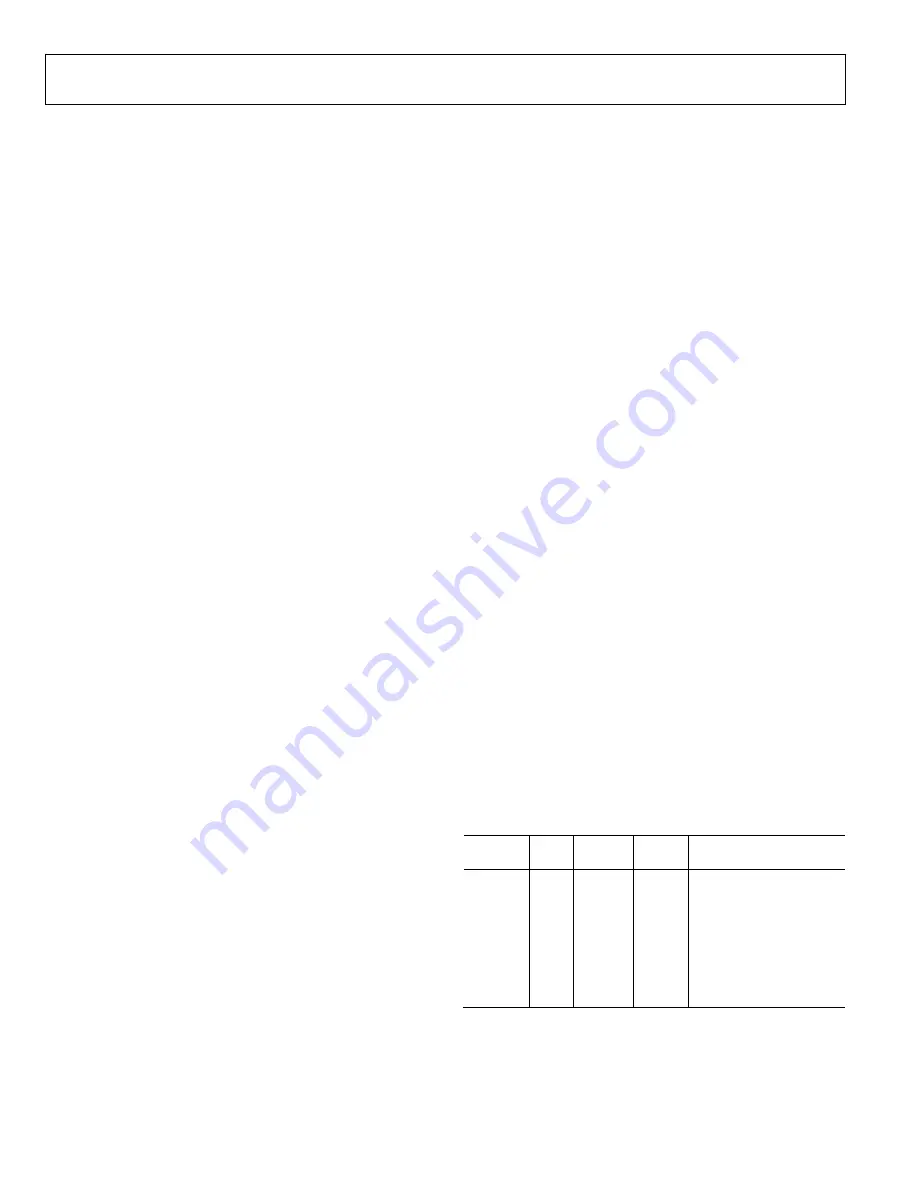

Table 1. ADDR Pin Configuration

I

2

C

Address

TDM

Slot

J11

(ADDR) J4

Configuration

0x14

1

GND

Open

ADDR pin connected

through 47 kΩ to GND

0x15

2

Open

Short

ADDR pin unconnected

0x16

3

IOVDD

Open

ADDR pin connected

through 47 kΩ to IOVDD

0x17

4

IOVDD

IOVDD ADDR pin directly

connected to IOVDD

N/A

1

N/A

1

GND

Short

Not an option

1

N/A means not applicable.

The SK1 10-pin header connects the USBi (provided with the kit)

for I

2

C control of the device.