UG-1870

Rev. 0 | Page 4 of 15

EVALUATION BOARD HARDWARE

DEVICE DESCRIPTION

The

is an 18-bit, 8-channel, simultaneous sampling,

successive approximation register (SAR) ADC. The device

operates from a single 4.75 V to 5.25 V power supply and

features throughput rates of up to 1 MSPS. The device has

1 MΩ input impedance for direct connection from the user

sensor outputs to the ADC.

HARDWARE LINK OPTIONS

Table 2 details the link option functions and the default power

link options. The EVAL-AD7606C18FMCZ can be powered by

different sources, as described in the Power Supplies section. By

default, the power supply required for the EVAL-

AD7606C18FMCZ comes from the

. The power supply

which generate the 5 V and 3.3 V supplies.

CONNECTORS AND SOCKETS

The connectors and sockets on the EVAL-AD7606C18FMCZ are

detailed in Table 1.

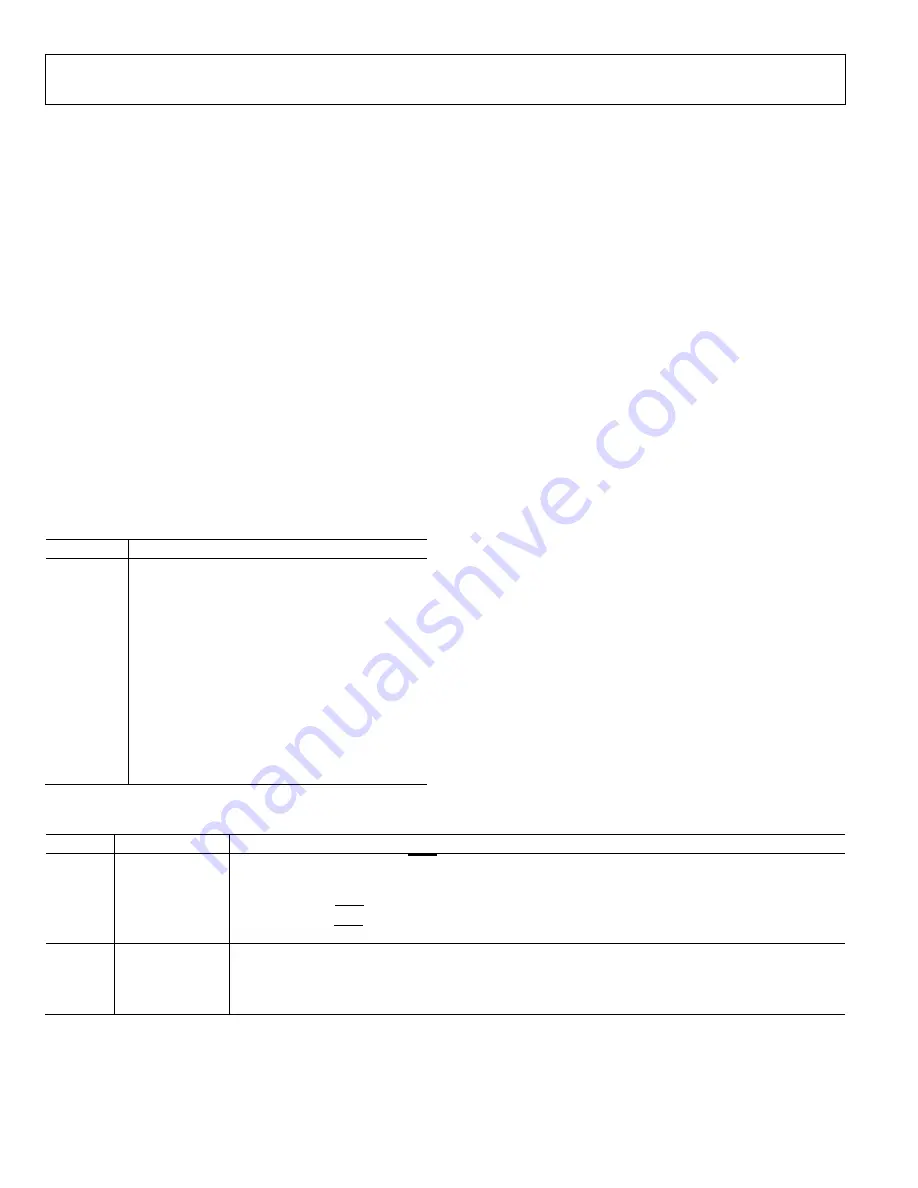

Table 1. On-Board Connectors

Connector

Function

J1 to J8

Analog input SMB connectors to Channel 1

through Channel 8

J9

Analog input SMB connector to external reference

P1, P2, P3

General connectors for debugging purposes or to

connect an external controller

P4

External power terminal block, 7 V to 9 V dc input

P5

External reference connection

P6, P8

8-pin connectors for input to Channel 1 through

Channel 4

P7, P11

Channel 8 surfboard evaluation headers

P9, P10

8-pin connectors for input to Channel 5 through

Channel 8

P12

FMC connector

The default interface to the EVAL-AD7606C18FMCZ is

achieved via the field programmable gate array (FPGA)

mezzanine card (FMC) connector, which connects the EVAL-

AD7606C18FMCZ to the SDP-H1.

POWER SUPPLIES

Before applying power and signals to the EVAL-

AD7606C18FMCZ, ensure that all link positions are set

according to the required operating mode. See Table 2 for the

complete list of link options.

The supply required for the EVAL-AD7606C18FMCZ comes

from the SDP-H1. Alternatively, the EVAL-AD7606C18FMCZ

can also be supplied with a dc power supply connected to the

P4 terminal block. Select the external power supply or the SDP-H1

supply through JP2. The power supply is then connected to the

on-board ADP7118 5 V and 3.3 V LDO linear regulators that

supply the proper bias to each of the various sections on the

EVAL-AD7606C18FMCZ.

CHANNEL INPUT

The J1 to J8 connectors allow the user to connect external

signals to the ADC channel inputs through the SMB inputs.

The EVAL-AD7606C18FMCZ is supplied with the AD7606C-18

mounted (U4, see Figure 1). The AD7606C-18 is an 8-channel

data acquisition system (DAS) with a simultaneous sampling

ADC. External signals can be applied to the P6, P8, P9, and P10

connectors on the EVAL-AD7606C18FMCZ.

Table 2. Link Options

Link

Default Position Function

JP1

A

The

software controls the STBY pin. When using the EVAL-AD7606C18FMCZ in standalone mode

without running the ACE software, JP1 allows the selection of standby mode. In this case, change the R8

and R10 resistors to 0 Ω links.

In Position A, the STBY pin is tied to V

DRIVE

.

In Position B, the STBY pin is tied to AGND.

JP2

A

JP2 selects the power supply source for the EVAL-AD7606C18FMCZ.

In Position A, the unregulated supply to the on-board LDOs is taken from the SDP-H1 12 V supply.

In Position B, the unregulated external supply to the on-board LDOs is taken from the P4 terminal block

connector.