ADM1060

Rev. B | Page 13 of 52

SFD FAULT TYPES

Three types of faults can be asserted by the SFD: an OV fault, a

UV fault, and an out-of-window fault (where the UV and OV

faults are OR’ed together). The type of fault required is

programmed using the fault type select bits (Bits 0, 1 in Register

_SnSEL). If an application requires separate fault conditions to

be detected on one supply (e.g., assert PDO1 if a UV fault

occurs on a 3.3 V supply, assert PDO9 if an OV fault occurs on

the same 3.3 V supply), that supply will need to be applied to

more than one input pin.

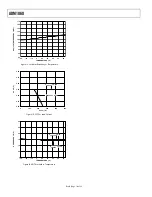

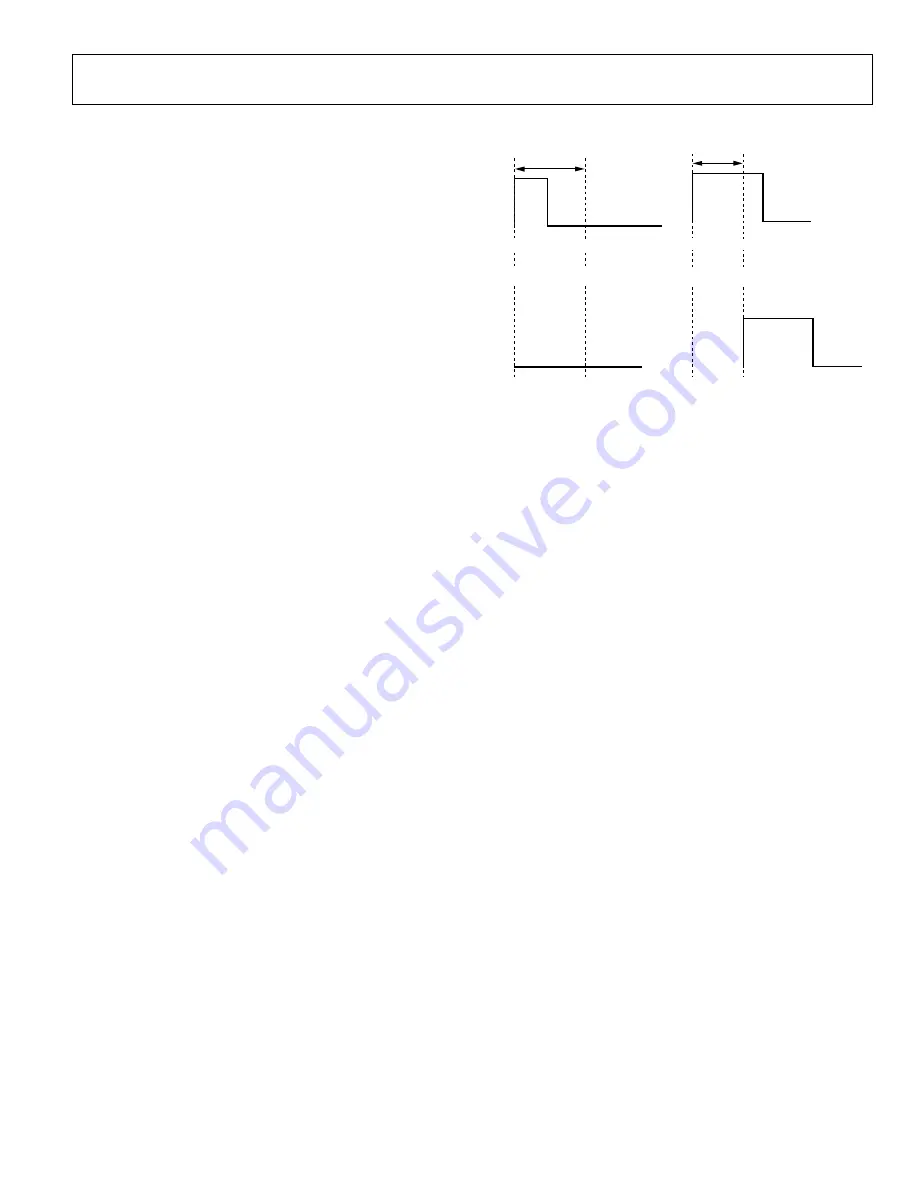

GLITCH FILTERING ON THE SFDs

The final stage of the SFD is a glitch filter. This block provides

time domain filtering on the output of the SFD. This allows the

user to remove any spurious transitions (such as supply bounce

at turn-on). This deglitching function is in addition to the

programmable hysteresis of the SFDs. The glitch filter timeout

is programmable up to 100 µs. If a pulse shorter than the

programmed timeout appears on the input, this pulse is masked

and the signal change will appear on the output. If an input

pulse longer than the programmed timeout appears on the

input, this pulse will appear on the output. The output will be

delayed (with respect to the input) by the length of the

programmed timeout.

Figure 19 shows the implementation of glitch filtering.

GLITCH FILTER INPUT

PROGRAMMED TIMEOUT

PROGRAMMED TIMEOUT

t

GF

t

GF

t

0

t

0

t

GF

t

GF

t

0

t

0

GLITCH FILTER OUTPUT

Figure 19. Glitch Filtering on the SFDs

PROGRAMMING THE SFDs ON THE SMBus

The details of using the SMBus are described later, but the regis-

ter names associated with the supply fault detector blocks, the

bit map of those registers, and the function of each of the bits is

described in the following tables. The tables show how to set up

UV threshold, UV hysteresis, OV threshold, OV hysteresis,

glitch filtering, and fault type for each of the SFDs on the

ADM1060.

Содержание ADM1060

Страница 51: ...ADM1060 Rev B Page 51 of 52 NOTES ...