–

14

–

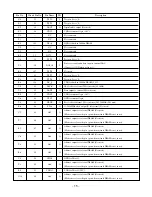

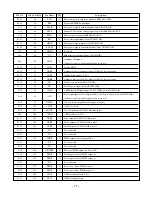

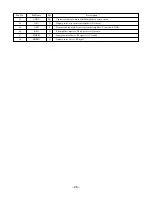

A-1

–

NC

–

Not connected.

A-2

–

NC

–

Not connected.

A-3

3

MNT1

O

Monitor output.

B-1

–

NC

–

Not connected.

B-2

–

NC

–

Not connected.

B-3

2

MNT0

I/O

Monitor input/output.

C-1

5

MNT3

O

Monitor output.

C-2

4

MNT2

O

Monitor output.

C-3

–

NC

–

Not connected.

D-1

7

SCLK

I

Microprocessor serial bus clock input.

D-2

6

SWDT

I

Microprocessor serial bus data writing input.

D-3

1

VDC0

–

VDD for internal logic (1.8V).

E-1

8

XLAT

I

Microprocessor serial bus latch input.

E-2

10

SRDT

O

Microprocessor serial bus data reading output.

E-3

11

SENS

O

Internal state output to the microprocessor serial bus address.

F-1

9

VSC0

–

GND for internal logic.

F-2

13

SQSY

O

ADIP synch output when PTGR (ADRS = $3B, DATA1 - D7) = 0.

DISC SUB-Q synch output when PTGR = 1.

F-3

12

XRST

I

Reset input. Reset with “L”.

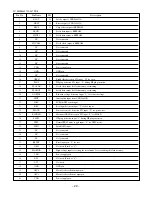

G-1

14

MTFLGL

O

Lch zero data detection flag output (Not used).

G-2

16

XINT

O

Interruption status output. “L” at interruption status.

G-3

15

TST1

I

Test pin. Set to “L”.

H-1

17

TST2

I

Test pin. Set to “L”.

H-2

19

OSCI

I

X’tal oscillation circuit input (OSCI pin reverse output).

H-3

18

VDIOSC

–

VDD for OSC cell (2.4V).

J-1

20

OSCO

O

X’tal oscillation circuit output.

J-2

–

NC

–

Not connected.

J-3

–

NC

–

Not connected.

K-1

21

VSIOSC

–

GND for OSC cell.

K-2

24

AOUTL

O

Built-in DAC Lch output.

K-3

25

DAV

DD

L

–

VDD for built-in DAC (Lch 2.4V).

L-1

22

DAV

SS

L

–

GND for built-in DAC (Lch).

L-2

23

VREFL

O

Built-in DAC VREF (Lch).

(Connect to GND via a capacitor of approximately 1

µ

F).

L-3

26

DAV

DD

R

–

VDD for built-in DAC (Rch 2.4V).

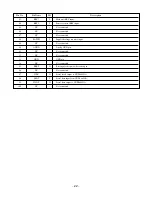

M-1

29

DAV

SS

R

–

GND for built-in DAC (Rch).

M-2

27

AOUTR

O

Internal DAC Rch output.

M-3

28

VREFR

O

Built-in DAC VREF (Rch) .

(Connect to GND via a capacitor of approximately 1

µ

F).

N-1

30

VSC1

–

GND for internal logic.

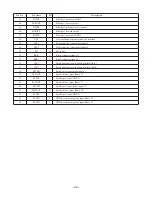

Pin No. Circuit Pin No. Pin Name I/O Description

IC, CXD2665GA

IC DESCRIPTION

N-2 31 XTSL I Swith input frequency of OSCI pin.(Connected to VDD)