28

Operation Theory

under heavy loading. Detailed function setup will be explained

in Section 4.2.2.

Note

:

When using waveform generation mode, all the four DACs in

the same D/A group must be configured for the same mode.

However, any one of the DAC can be disabled. If users need

to use the software update mode, they can use another D/A

group on the PXI/DAQ-2502.

Setting up the DACs

Before using the DACs, users should setup the reference

source and its polarity. Each DAC has its own reference and

polarity settings. For ex-ample; the internal voltage reference of

D/A Group A is tied to in10V, however, users can still

connect external reference thru AOEXTREF (pin 5 on CN2), for

example to a +3.3V voltage source. Therefore, each DAC in D/

A Group A has two reference options: 10V or 3.3V. However,

DA update timing, trigger Source, and trigger/stop mode are all

the same throughout that D/A Group.

DAQ/PXI-2500 SERIES provides the capability to fine tune the

voltage reference from the external source. The external refer-

ence is fed thru an on board calibrated circuit, with programma-

ble offset. Users can utilize this capability to generate precise

D/A outputs.

CAUTION

: The range of external voltage reference should be within

±10V.

Utilizing Multiplying Characteristic of DACs

The D/A reference selection let users fully utilize the multiplying

charac-teristics of the DACs. Digital codes sent to the D/A con-

verters will be multiplied by the reference to generate output.

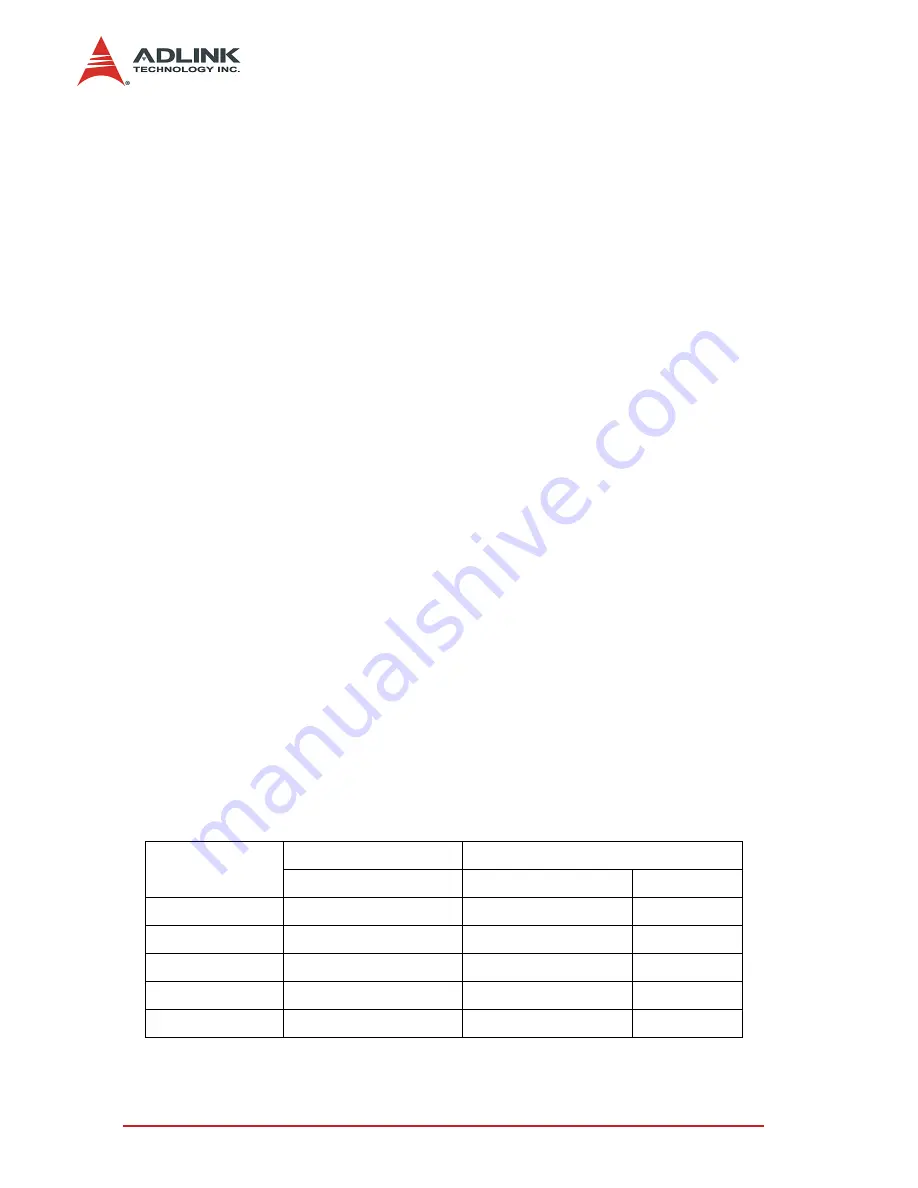

Magnitude

Bipolar

Unipolar

Output

Output

Digital Code

FSR – LSB

+Vref * (2046 / 2048) Vref * (4095 / 4096)

0FFF

Mi LSB

+Vref * (1 / 2048)

Vref * (2049 4096)

0801

Midscale

0

Vref * (2048 / 4096)

0800

Midscale – LSB

-Vref * ( 1 / 2048)

Vref * (2047 / 4096)

07FF

Table 4-5: D/A Output Versus Digital Codes

Содержание NuDAQ-2500 Series

Страница 4: ......

Страница 16: ...8 Introduction...

Страница 24: ...16 Signal Connections...

Страница 31: ...Operation Theory 23 Figure 4 2 Post trigger Figure 4 3 Delay trigger...

Страница 41: ...Operation Theory 33 Figure 4 9 Post Trigger Generation Figure 4 10 Delay Trigger Generation...