Introduction

7

X

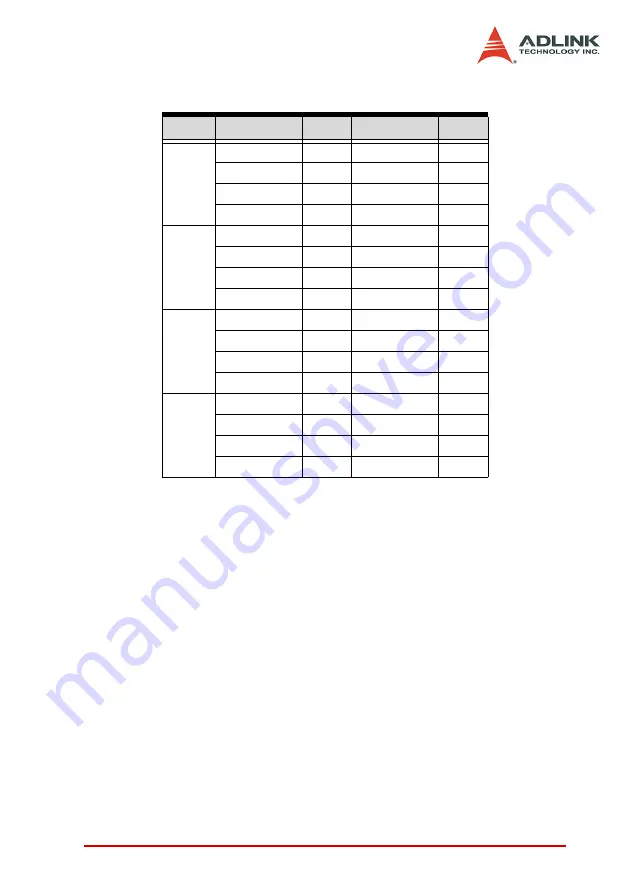

CMRR: (DC to 60Hz, Typical)

X

Time-base source:

Z

Internal 40MHz or External clock Input (fmax: 40MHz,

fmin: 1MHz, 50% duty cycle)

X

Trigger modes:

Z

Post-trigger, Delay-trigger, Pre-trigger and Middle-trigger

X

Data transfers:

Z

Programmed I/O, and bus-mastering DMA with scatter/

gather

X

Input coupling: DC

X

Offset error:

Z

Before calibration: ±60mV max

Z

After calibration: ±1mV max

X

Gain error:

Device Input Range CMRR Input Range CMRR

2010

±10V 90

dB

0~10V

89

dB

±5V

92 dB

0~5V

92 dB

±2.5V

95 dB

0~2.5V

94 dB

±1.25V

97 dB

0~1.25V

97 dB

2005

±10V 86

dB

0~10V

85

dB

±5V

88 dB

0~5V

88 dB

±2.5V

91 dB

0~2.5V

90 dB

±1.25V

93 dB

0~1.25V

93 dB

2006

±10V 87

dB

0~10V

86

dB

±5V

89 dB

0~5V

88 dB

±2.5V

91 dB

0~2.5V

91 dB

±1.25V

93 dB

0~1.25V

93 dB

2016

±10V

85dB

0~10V

86dB

±5V

88dB

0~5V

88dB

±2.5V

91dB

0~2.5V

92dB

±1.25V

95dB

0~1.25V

95dB

Table 1-3: CMRR: (DC to 60Hz)

Содержание DAQ/PXI-20 Series

Страница 5: ......

Страница 11: ......

Страница 81: ...70 Operation Theory VHDCI Connecting them to any signal source may cause per manent damage ...