Series AVME9125 VMEbus 6U Analog Input Board

___________________________________________________________________________________________

- 5 -

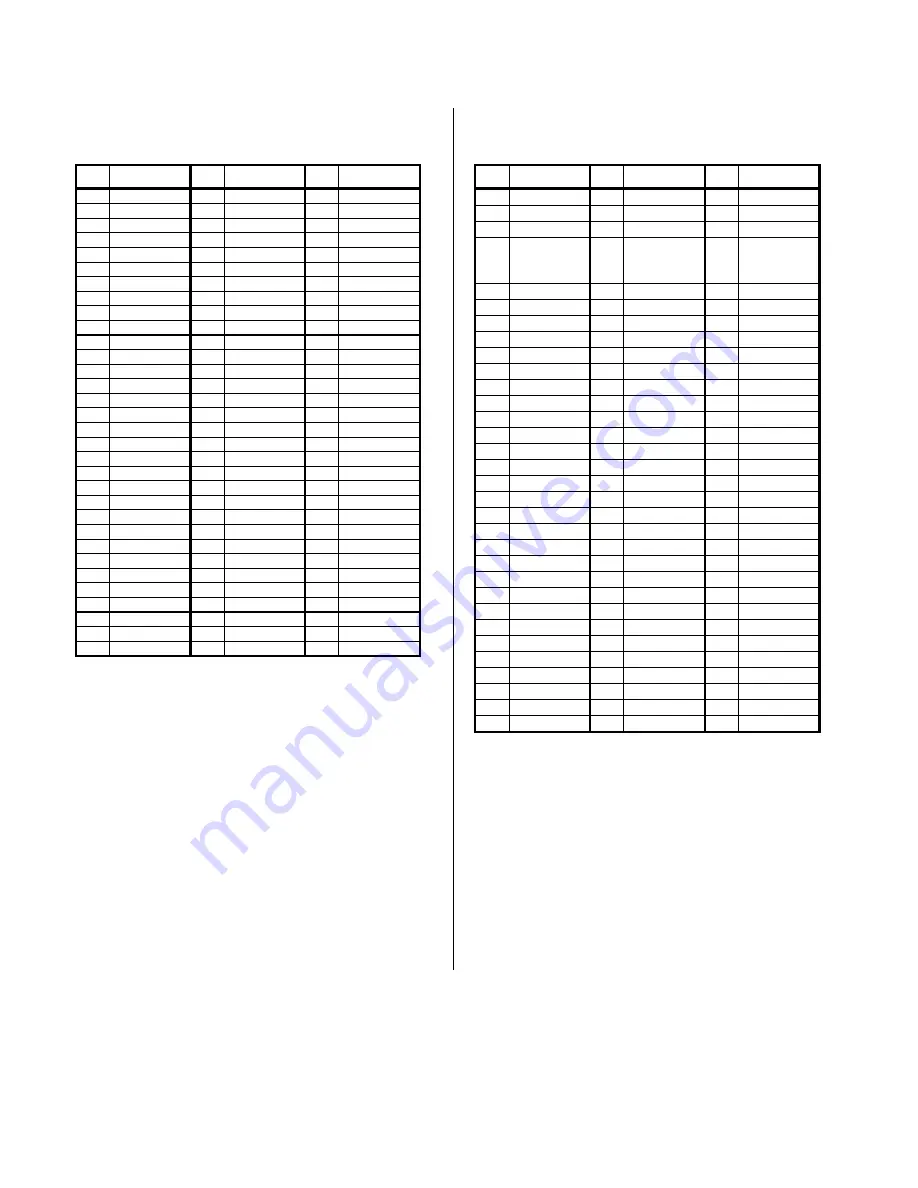

Pin assignments for the P1 connectors of the AVME9125 are

shown in Table 2.2:

TABLE 2.2: VMEbus P1 CONNECTIONS

Pin

Description

Pin

Description

Pin

Description

1A

D00

1B

BBSY*

1C

D08

2A

D01

2B

BCLR*

2C

D09

3A

D02

3B

ACFAIL*

3C

D10

4A

D03

4B

BG0IN*

4C

D11

5A

D04

5B

BG0OUT*

5C

D12

6A

D05

6B

BG1IN*

6C

D13

7A

D06

7B

BG1OUT*

7C

D14

8A

D07

8B

BG2IN*

8C

D15

9A

GND

9B

BG2OUT*

9C

GND

10A

SYSCLK

10B

BG3IN*

10C

SYSFAIL*

11A

GND

11B

BG3OUT*

11C

BERR*

12A

DS1*

12B

BR0*

12C SYSRESET*

13A

DS0*

13B

BR1*

13C

LWORD*

14A

WRITE*

14B

BR2*

14C

AM5

15A

GND

15B

BR3*

15C

A23

16A

DTACK*

16B

AM0

16C

A22

17A

GND

17B

AM1

17C

A21

18A

AS*

18B

AM2

18C

A20

19A

GND

19B

AM3

19C

A19

20A

IACK*

20B

GND

20C

A18

21A

IACKIN*

21B

SERCLK

21C

A17

22A

IACKOUT*

22B

SERDAT*

22C

A16

23A

AM4

23B

GND

23C

A15

24A

A07

24B

IRQ7*

24C

A14

25A

A06

25B

IRQ6*

25C

A13

26A

A05

26B

IRQ5*

26C

A12

27A

A04

27B

IRQ4*

27C

A11

28A

A03

28B

IRQ3*

28C

A10

29A

A02

29B

IRQ2*

29C

A09

30A

A01

30B

IRQ1*

30C

A08

31A

-12V

31B

+

5V STDBY

31C

+12V

32A

+5V

32B

+5V

32C

+5V

Asterisk (*) is used to indicate an active-low signal.

BOLD ITALIC

Logic Lines are NOT USED by the board.

The P2 connector provides the analog input interface for the

AVME9125 and the companion Expander board (EXP9125). The

P2 pin assignments are given in Table 2.3. When reading Table

2.3 note that channel designations are abbreviated to save space.

For example channel 0 plus input is abbreviated CH0+.

Channels 0 to 15 are input direct to the AVME9125 while

channels 16 to 31 are multiplexed on the EXP9125 board and a

single input pair signals and Analog- are connected for

input to the AVME9125 via the P2.

Pins 1 to 6 of rows A and C are used to interface to the

EXP9125. Signals CHSel3 to CHSel0 are used to control an

analog multiplexer for selection of one of channels 16 to 31.

Signal CHSel0 also serves to indicate the presence of the

EXP9125 to the AVME9125. The EXP9125 will pull CHSel0 high

when present. Lastly, the AVME9125 provides

±

15 volts to the

EXP9125 via the P2 connector.

Pin assignments for the P2 connectors of the AVME9125 are

shown in Table 2.3:

Table 2.3: AVME9125 P2 Pin Assignments

Pin

Description

Pin

Description

Pin

Description

1A

ChSel3

1B

Not Used

1C

Ground

2A

ChSel2

2B

Not Used

2C

3A

ChSel1

3B

Not Used

3C

Analog-

4A

ChSel0/

EXP9125

Present

4B

Not Used

4C

Ground

5A

Autoz/Ch_

5B

Not Used

5C

Ground

6A

+15V DC

6B

Not Used

6C

-15V DC

7A

Not Used

7B

Not Used

7C

Not Used

8A

Not Used

8B

Not Used

8C

Shield

9A

Analog Com 9B

Not Used

9C

Analog Com

10A

CH14-

10B

Not Used

10C

CH15-

11A

CH14+

11B

Not Used

11C

CH15+

12A

Analog Com 12B

Not Used

12C

Analog Com

13A

CH12-

13B

Not Used

13C

CH13-

14A

CH12+

14B

Not Used

14C

CH13+

15A

Analog Com 15B

Not Used

15C

Analog Com

16A

CH10-

16B

Not Used

16C

CH11-

17A

CH10+

17B

Not Used

17C

CH11+

18A

Analog Com 18B

Not Used

18C

Analog Com

19A

CH8-

19B

Not Used

19C

CH9-

20A

CH8+

20B

Not Used

20C

CH9+

21A

Analog Com 21B

Not Used

21C

Analog Com

22A

CH6-

22B

Not Used

22C

CH7-

23A

CH6+

23B

Not Used

23C

CH7+

24A

Analog Com 24B

Not Used

24C

Analog Com

25A

CH4-

25B

Not Used

25C

CH5-

26A

CH4+

26B

Not Used

26C

CH5+

27A

Analog Com 27B

Not Used

27C

Analog Com

28A

CH2-

28B

Not Used

28C

CH3-

29A

CH2+

29B

Not Used

29C

CH3+

30A

Analog Com 30B

Not Used

30C

Analog Com

31A

CH0-

31B

Not Used

31C

CH1-

32A

CH0+

32B

Not Used

32C

CH1+

POWER-UP TIMING AND LOADING

The AVME9125 board uses Field Programmable Gate-Arrays

(FPGA) to handle the bus interface and control logic timing. Upon

power-up, the FPGAs automatically clocks in configuration vectors

from a local serial PROM to initialize the logic circuitry for normal

operation. This time is measured as the first 145mS (typical) after

the +5 Volt supply rises to +2.5 Volts at power-up. The VMEbus

specification requires that the bus master drive the system reset

for the first 200mS after power-up, thus inhibiting any data

transfers from taking place.

IP control registers are also reset following a power-up

sequence, disabling interrupts, etc. (see Section 3 for details).

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com