Preliminary Product Information

This document contains information for a new product.

Cirrus Logic reserves the right to modify this product without notice.

Copyright

©

Cirrus Logic, Inc. 2005

(All Rights Reserved)

Cirrus Logic, Inc.

http://www.cirrus.com

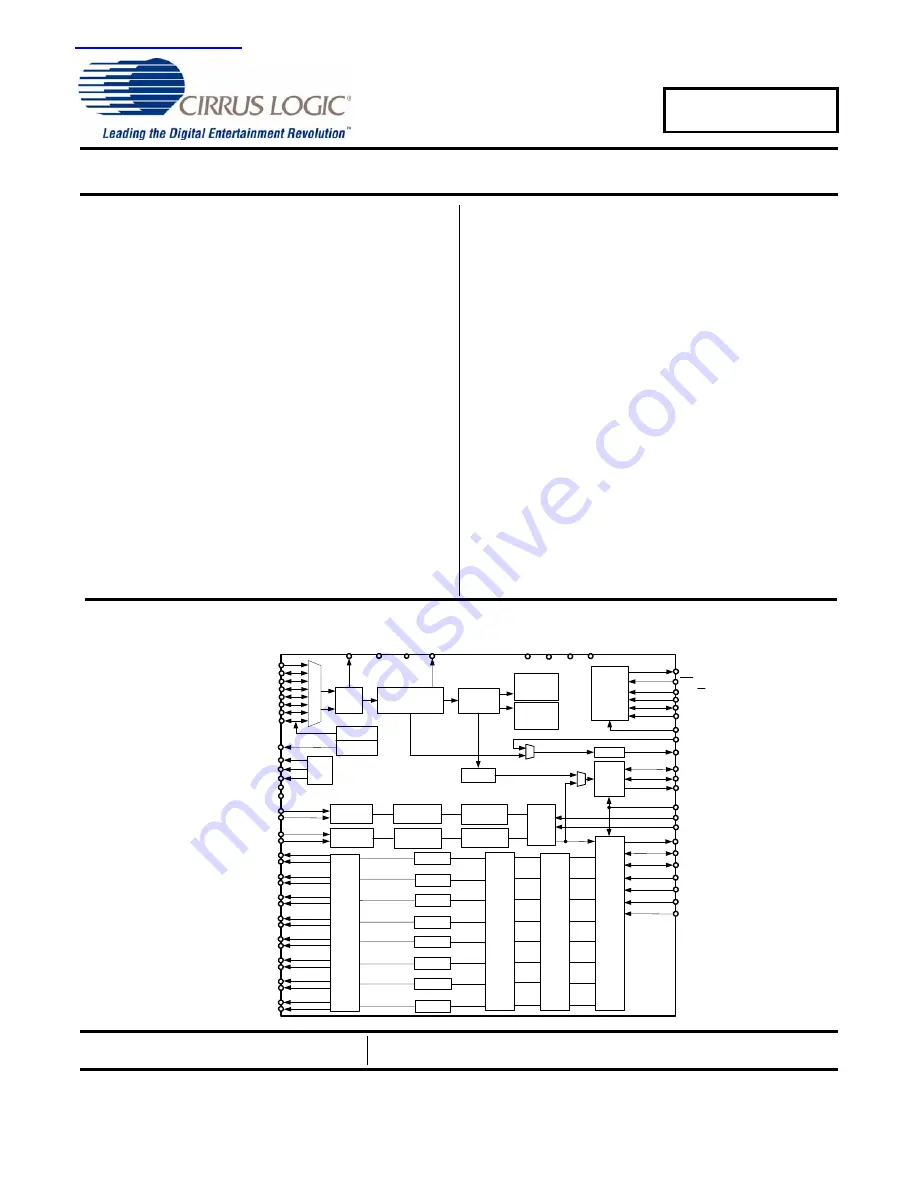

CS42528

114 dB, 192 kHz 8-Ch Codec with S/PDIF Receiver

Features

z

Eight 24-bit D/A, two 24-bit A/D Converters

z

114 dB DAC / 114 dB ADC Dynamic Range

z

-100 dB THD+N

z

System Sampling Rates up to 192 kHz

z

S/PDIF Receiver Compatible with EIAJ CP1201

and IEC-60958

z

Recovered S/PDIF Clock or System Clock

Selection

z

8:2 S/PDIF Input MUX

z

ADC High-pass Filter for DC Offset Calibration

z

Expandable ADC Channels and One-line Mode

Support

z

Digital Output Volume Control with Soft Ramp

z

D/-15dB Input Gain Adjust for ADC

z

Differential Analog Architecture

z

Supports logic levels between 5 V and 1.8 V.

General Description

The CS42528 codec provides two analog-to-digital and eight

digital-to-analog delta-sigma converters, as well as an integrat-

ed S/PDIF receiver, in a 64-pin LQFP package.

The CS42528 integrated S/PDIF receiver supports up to eight

inputs, clock recovery circuitry and format auto-detection. The

internal stereo ADC is capable of independent channel gain

control for single-ended or differential analog inputs. All eight

channels of DAC provide digital volume control and differential

analog outputs. The general purpose outputs may be driven

high or low, or mapped to a variety of DAC mute controls or

ADC overflow indicators.

The CS42528 is ideal for audio systems requiring wide dynam-

ic range, negligible distortion and low noise, such as A/V

receivers, DVD receivers, digital speaker and automotive audio

systems.

ORDERING INFORMATION

CS42528-CQZ

-10° to 70° C

64-pin LQFP

Lead Free

CS42528-DQZ

-40° to 85° C

64-pin LQFP

Lead Free

CDB42528

Evaluation Board

RST

RXP0

RXP1/G PO 1

AD0/CS

SCL/CCLK

SDA/C DO UT

AD 1/C DIN

VLC

AO UT A1+

AO UT A1-

AO U TB1+

AO U TA3+

AO UT A3-

AO UT A2-

AO U TB2-

AO U TA2+

AO UT B2+

AO UTB1-

AO U TB3+

AO UTB3-

AO UT A4+

AO U TA4-

AO UT B4+

AO UT B4-

AINL+

AINL-

AIN R+

AINR -

F ILT+

REFG ND

VQ

Ref

ADC#1

ADC #2

Digital Filter

Digital Filter

G ain & C lip

G ain & Clip

CX_SDO UT

AD CIN1

ADC IN2

CX_SCLK

CX_LRC K

CX_SDIN4

CX_SD IN 3

CX_SDIN2

CX_SDIN1

VLS

SAI_LRC K

SAI_SCLK

SAI_SDO UT

D G ND

VD

O M CK

RM CK

LPF LT

T XP

IN T

Rx

Clock/D ata

Recovery

S/PDIF

Decoder

DEM

Serial

Audio

Interface

Port

C&U Bit

Data Buffer

Control

Port

DAC #1

D AC #2

DAC#3

D AC #4

DAC#5

DAC#6

DAC#7

DAC #8

D

ig

it

a

l

F

il

te

r

V

o

lu

m

e

C

o

n

tr

o

l

DG N D

RXP2/G PO 2

RXP3/G PO 3

RXP4/G PO 4

RXP5/G PO 5

RXP6/G PO 6

RXP7/G PO 7

VD

M UTEC

G PO

M UTE

A

n

a

lo

g

F

il

te

r

VARX

AG ND

ADC

Serial

Data

AG ND

VA

Internal M CLK

CO D EC

Serial

Port

M ult/Div

F orm at

Detector

JAN ‘05

DS586PP5