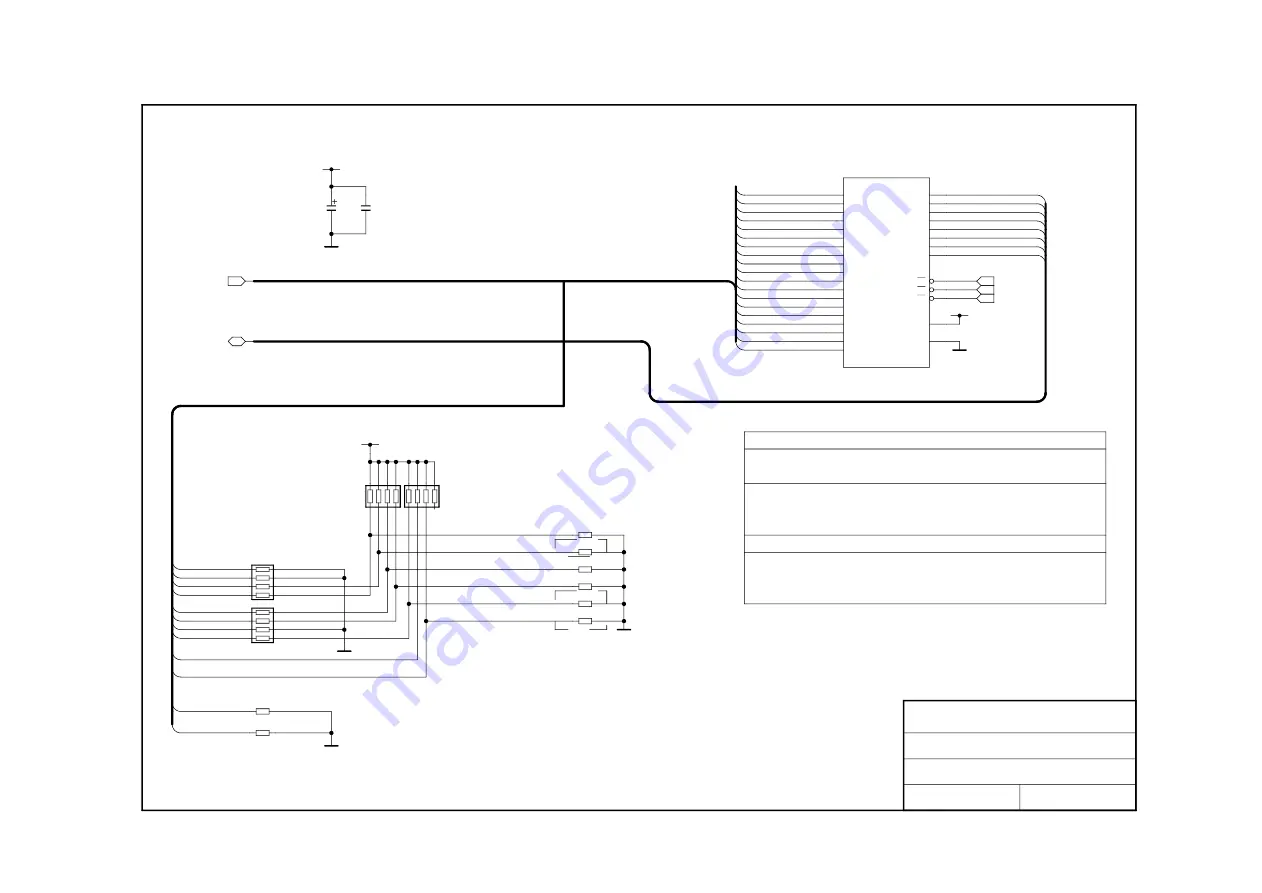

1.0

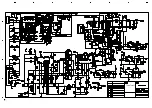

CPU

203-L37R70-01DL

10: LOW(Use TCLK)

11: LOW (set all display out to ’0’)

12: LOW

13: LOW (disable serial interface debug)

14: LOW

15: LOW

16: HIGH(use crystal)

17: LOW (8bit bus with OCM access external ROM

18: HIGH

19: LOW

BOOTSTRAO HEADER

OPEN=1

SHUNTED=0

XOCECO

XIAMEN OVERSEAS CHINESE

ELECTRONIC CO., LTD.

TITLE:

DWG NO.

REV.

Sheet 6 of 7

Socket for a X8 Flash (64/128/256/512K)

and PROMJETmemory Emulater

Memory I/F

OCMADDR[16]

Custom1

Custom2

SerialInterfaceDebug1

SerialInterfaceDebug2

SerialInterfaceDebug3

OCMADDR[18]

OCMADDR[17]

OCMADDR[19]

OCMADDR[0-19]

OCMADDR[8]

OCMADDR[13]

OCMADDR[14]

OCMADDR[12]

OCMADDR[15]

OCMADDR[10]

OCMADDR[0-19]

OCMDATA[0-7]

OCMADDR[18]

OCMADDR[17]

OCMADDR[16]

OCMADDR[15]

OCMADDR[14]

OCMADDR[13]

OCMADDR[12]

OCMADDR[10]

OCMADDR[9]

OCMADDR[8]

OCMADDR[7]

OCMADDR[6]

OCMADDR[5]

OCMADDR[4]

OCMADDR[3]

OCMADDR[2]

OCMADDR[1]

OCMADDR[0]

OCMDATA[7]

OCMDATA[6]

OCMDATA[5]

OCMDATA[4]

OCMDATA[3]

OCMDATA[2]

OCMDATA[1]

OCMDATA[0]

OCMADDR[9]

OCMADDR[11]

OCMADDR[11]

R163

10K

R164

10K

R159

10K

R160

10K

R165

0

R166

0

R167

0

R168

0

R169

0

R170

0

R161

10K

R162

10K

/ROM_CS

/OCM_RE

/OCM_WE

OCMADDR[0-19]

OCMDATA[0-7]

C233

100n

C232

22uF

10V

N17

MX29LV040-PLCC

22

CE

1

A18

11

A1

31

WE

3

A15

8

A4

6

A6

30

A17

23

A10

29

A14

7

A5

5

A7

26

A9

9

A3

24

OE

10

A2

25

A11

4

A12

27

A8

32

VCC

2

A16

28

A13

12

A0

21

Q7

13

Q0

14

Q1

19

Q5

20

Q6

15

Q2

18

Q4

16

GND

17

Q3

+3.3V_DIG

+3.3V_DIG

+3.3V_DIG

INT_OSC

8-BIT_FLASH

8-BIT_FLASH1

8-BIT_FLASH3

5

5

5

5

5

Summary of Contents for PH-42R6

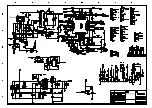

Page 1: ...PDP TELEVISION PH 42R6 Canada...

Page 11: ...9 Fig 1 1 Simplified functional block diagram of the MSP 34x0G...

Page 13: ...11 INTERNAL BLOCK DIAGRAM...

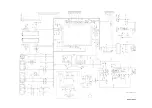

Page 26: ...Power board...

Page 27: ...Power board power board...

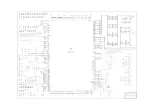

Page 39: ...APPENDIX Exploded view PH 42X6...

Page 42: ...603 PH42R60 10 Ver 1 0...