Virtex-6 Getting Started Guide

61

UG533 (v1.4) November 15, 2010

Installing the ISE Software

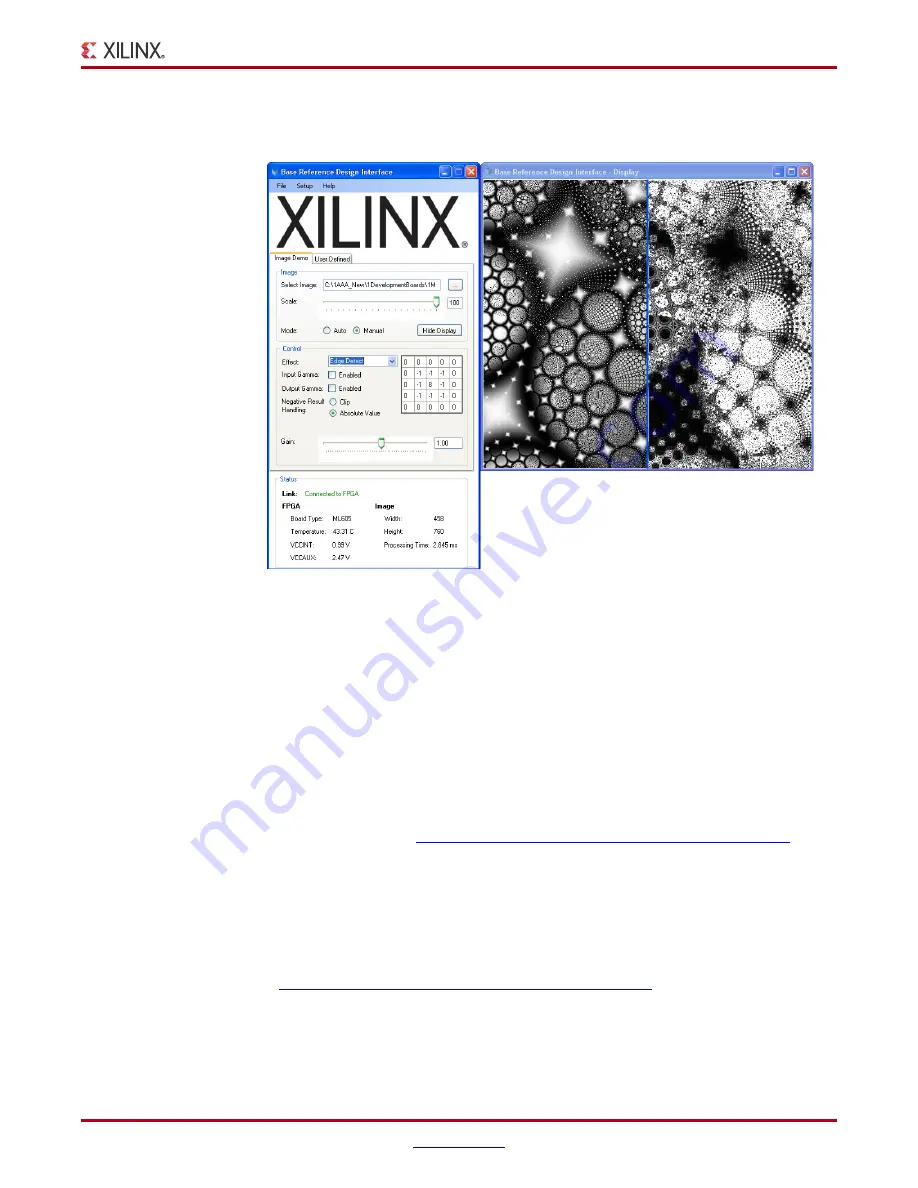

Choose Edge Detect from the effect menu. The filtering transform shown in

will be displayed.

Different effects can be set automatically by selecting the

Auto

mode button.

FPGA temperature, VCCINT, VCCAUX, Image dimensions, and processing time are also

reported by the Status field.

You have now completed running the reference design.

Installing the ISE Software

The ML605 evaluation kit includes entitlement to a seat that permits the

ISE Design Suite: Logic Edition to be used with a Virtex-6 XC6VLX240T-1FFG1156C FPGA.

This software can be installed from the DVD provided with the kit. The latest version can

also be downloaded from

http://www.xilinx.com/support/download/index.htm

The ML605 evaluation kit also works with the software listed here:

•

ISE Design Suite: Embedded Edition

•

ISE Design Suite: DSP Edition

•

ISE Design Suite: System Edition

Update the software before working with the evaluation kit. Updates can be downloaded

from

http://www.xilinx.com/support/download/index.htm

To install the ISE Design Suite: Logic Edition software from the DVD included with the

ML605 evaluation kit:

1.

Activate the software license. See

“Redeeming the Software and IP License.”

X-Ref Target - Figure 1-60

Figure 1-60:

Original and FPGA Filtered Images using Edge Detect Effect