1

1

2

2

3

3

4

4

D

D

C

C

B

B

A

A

Date:

Page

3

of

5

Number:

Title:

01

Rev.

A4

Copyright:

Trenz Electronic GmbH

FPGA.SchDoc

Filename:

2018-05-25

Default

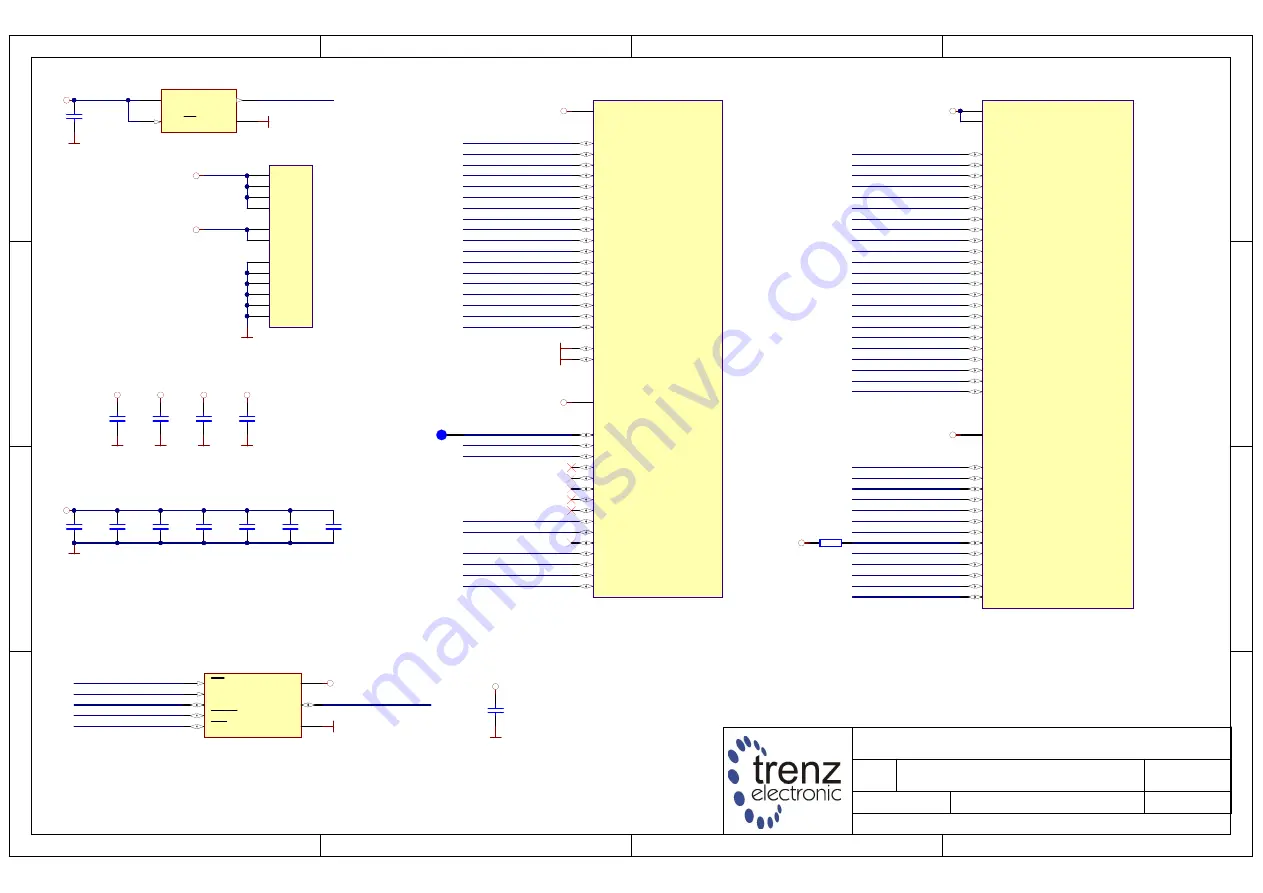

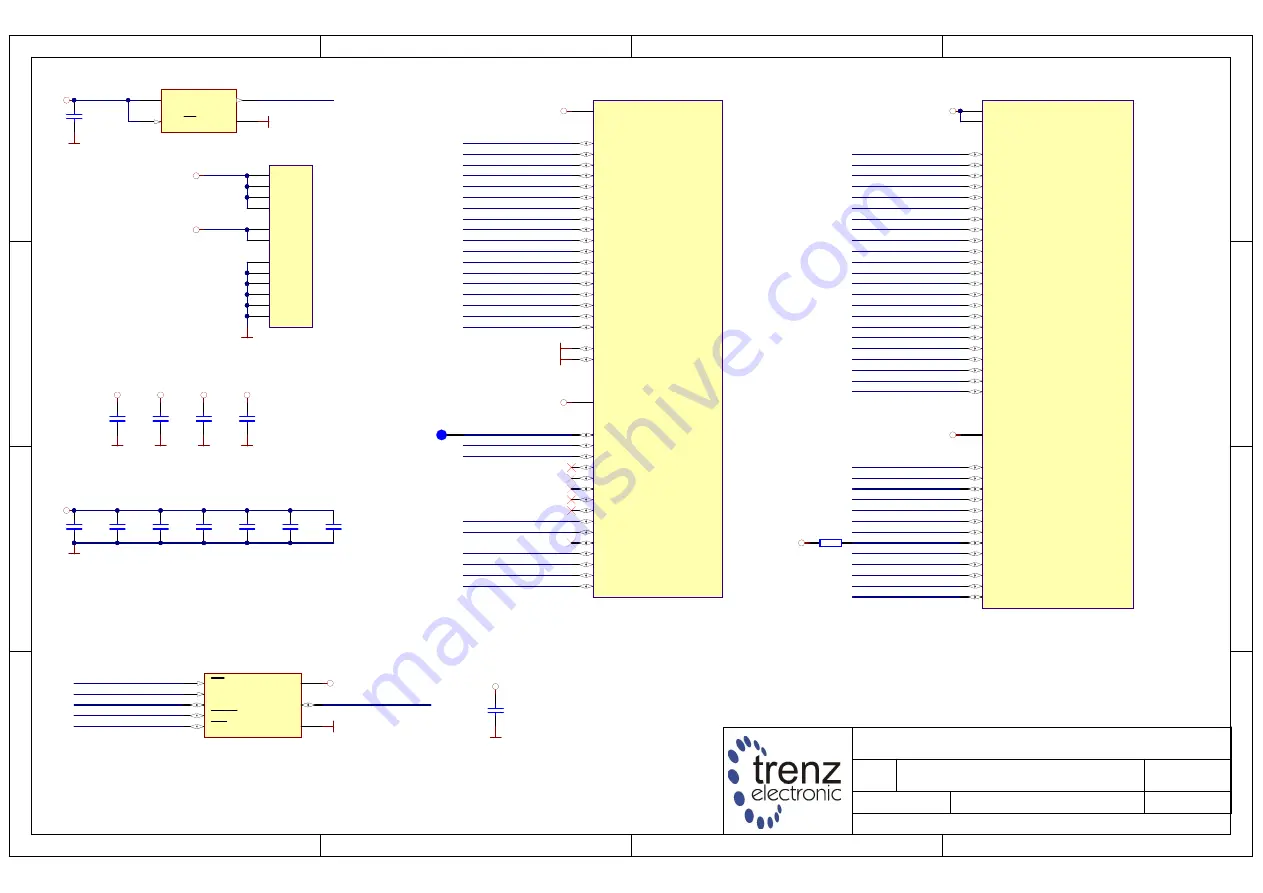

TEC0117

OE/ST

1

GND

2

CLK

3

VDD

4

U6

SiT8008BI-73-XXS-100.000000E

CLK_X

3.3V

GND

25V

X5R

C24

100nF

GND

IOR11A/MI/D7

62

IOR11B/MO/D6

61

IOR12A/MCS_N/D5

60

IOR12B/MCLK/D4

59

IOR13A/FASTRD_N/D3

57

IOR14A/SO/D1

56

IOR14B/SSPI_CS_N/D0

55

IOR15A/DIN/CLKHOLD_N

54

IOR15B/DOUT/WE_N

53

IOR17A/GCLKT_3

52

IOR17B/GCLKC_3

51

IOR22B

50

IOR24A

49

IOR24B

48

IOR5A/RPLL_T_in

63

IOT10A

84

IOT10B

83

IOT11A

82

IOT11B

81

IOT12A

80

IOT12B

79

IOT37A

77

IOT37B

76

IOT38A

75

IOT38B

74

IOT39A

73

IOT39B

72

IOT41A

71

IOT41B

70

IOT42A

69

IOT42B

68

IOT8A

86

IOT8B

85

MODE0

88

MODE1

87

VCCO0

67

VCCO1

58

U1A

GW1NR-LV9QN88C6/I5

IOB11A

27

IOB11B

28

IOB13A

29

IOB13B

30

IOB17A

31

IOB17B

32

IOB23A

33

IOB23B

34

IOB29A/GCLKT_4

35

IOB29B/GCLKC_4

36

IOB2A

17

IOB2B

18

IOB31A

37

IOB31B

38

IOB33A

39

IOB33B

40

IOB41A

41

IOB41B

42

IOB43B

47

IOB4A

19

IOB4B

20

IOB8A

25

IOB8B

26

IOL11A/TMS

5

IOL11B/TCK

6

IOL12B/TDI

7

IOL13A/TDO

8

IOL13B/RECONFIG_N

9

IOL14A/DONE

10

IOL15A/GCLKT_6

11

IOL22A

13

IOL22B

14

IOL26A

15

IOL26B

16

IOL2A

3

IOL5A/JTAGSEL_N/LPLL_T_in

4

VCCO2

23

VCCO2

44

VCCO3

12

U1B

GW1NR-LV9QN88C6/I5

VCC

22

VCC

66

VCC

1

VCC

45

VCCX

64

VCCX

78

VSS

2

VSS

46

VSS

21

VSS

24

VSS

43

VSS

65

U1C

G

W

1

N

R

-L

V

9

Q

N

8

8

C

6

/I

5

3.3V

3.3V

3.3V

3.3V

GND

TMS

TDI

TDO

TCK

JTAGEN

BDBUS1

BDBUS2

BDBUS3

BDBUS4

BDBUS5

BDBUS0

D6

D7

D8

D9

D10

D11

D12

D13

D14

LED1

LED2

LED3

LED4

LED5

LED6

LED7

LED8

D12_R

D11_R

CONF_DONE

AIN0

AIN1

AIN2

AIN3

AIN4

AIN5

AIN6

AREF

D0

D1

D2

D3

D4

D5

CLK_X

GND

GND

PIO_05

PIO_06

PIO_07

PIO_08

PIO_01

PIO_02

PIO_03

PIO_04

CLK12M

3.3V

1.2V

1.2V

25V

X5R

C15

100nF

25V

X5R

C16

100nF

25V

X5R

C18

100nF

1.2V

1.2V

1.2V

GND

GND

GND

GND

1%

R3

2K

3.3V

3.3V

6.3V

X5R

C2

4.7µF

25V

X5R

C3

100nF

25V

X5R

C4

100nF

25V

X5R

C10

100nF

GND

25V

X5R

C21

100nF

25V

X5R

C22

100nF

6.3V

X5R

C14

4.7µF

25V

X5R

C25

100nF

USER_BTN

RESET

HOLD/IO3

7

VCC

8

CS

1

SO/IO1

2

WP/IO2

3

GND

4

SI/IO0

5

CLK

6

U2

W74M64FVSSIQ

3.3V

GND

F_CS

F_CLK

F_SI

F_IO3

F_IO2

F_SO

F_CS

F_CLK

F_SI

F_IO3

F_IO2

F_SO

25V

X5R

C27

100nF

GND

3.3V

TP7

Testpoint 0.8mm