TXZ Family

Flash Memory

2018-06-05

80 / 120

Rev. 2.0

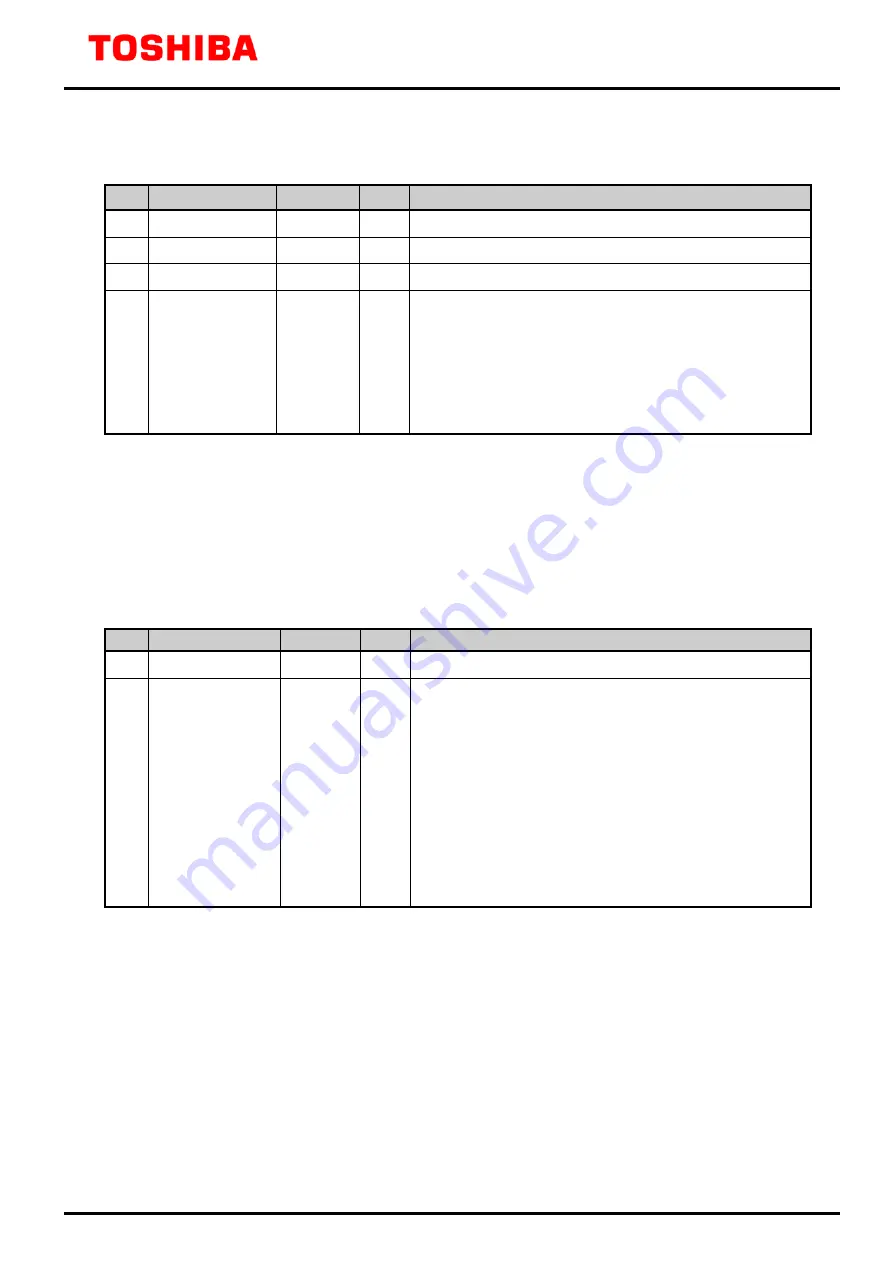

5.2.20. [FCBNKCR] (Flash Bank Change Register)

Bit

Bit Symbol

After reset

Type

Function

31:7

-

0

R

Read as “0”

6:4

-

000

R/W Write as “000”

3

-

0

R

Read as “0”

2:0

BANK0[2:0]

000

R/W

Address “0x5E005000” to “0x5E005FFF” of code flash

change to the user information area.

111

:

User information area

000

:

Code Flash

Others

:

Don’t care

Note 1: Before and after BANK0 operation, code flash buffer operation is required. For detail, refer to

Flash Buffer Disable and Clear Register”.

Note 2: To set this register, write the value to the register, and confirm the written value by reading the register.

Note 3: Rewrite the contents of this register on the program code in the RAM.

Note 4: Do not access to code flash (Area0) except “0x5E005000” to “0x5E005FFF” while the user information

area is being used.

5.2.21. [FCBUFDISCLR] Flash Buffer Disable and Clear Register

Bit

Bit Symbol

After reset

Type

Function

31:3

-

0

R

Read as “0”

2:0 BUFDISCLR[2:0]

000

R/W

Stops the buffer of code flash, and clears the buffer.

111: Stops the buffer function and clears the buffer.

000: Start the buffer function.

Others: Inactive

When bank switch (

[FCBNKCR]

) is performed between

code flash (Area 0) and user information area, make sure

to stop and clear the buffer with this register before the

switching starts. After the user information area is

operated, make sure to write “000” to start the buffer

operation.

Note1: When the value is set to this register, write the value to the register, and confirm the written value by

reading the register.

Note2: Rewrite the contents of this register on the program code in the RAM.