EVM Assembly Drawing and PCB Layout

www.ti.com

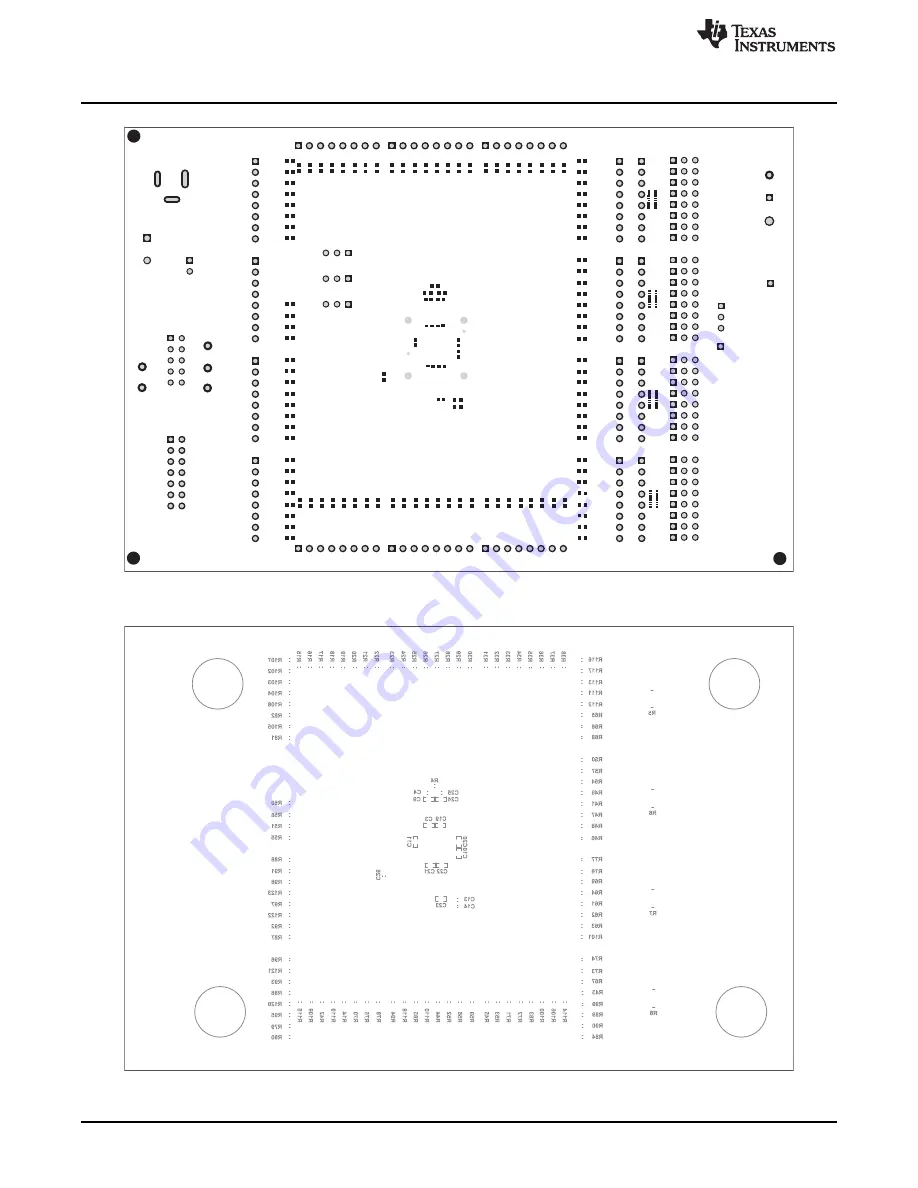

Figure 14. UCD90240EVM-704 Bottom Solder Mask

Figure 15. UCD90240EVM-704 Bottom Overlay

22

UCD90240EVM-704 24-Rail Sequencer Development Board

SLVUAF3A – March 2015 – Revised March 2015

Submit Documentation Feedback

Copyright © 2015, Texas Instruments Incorporated