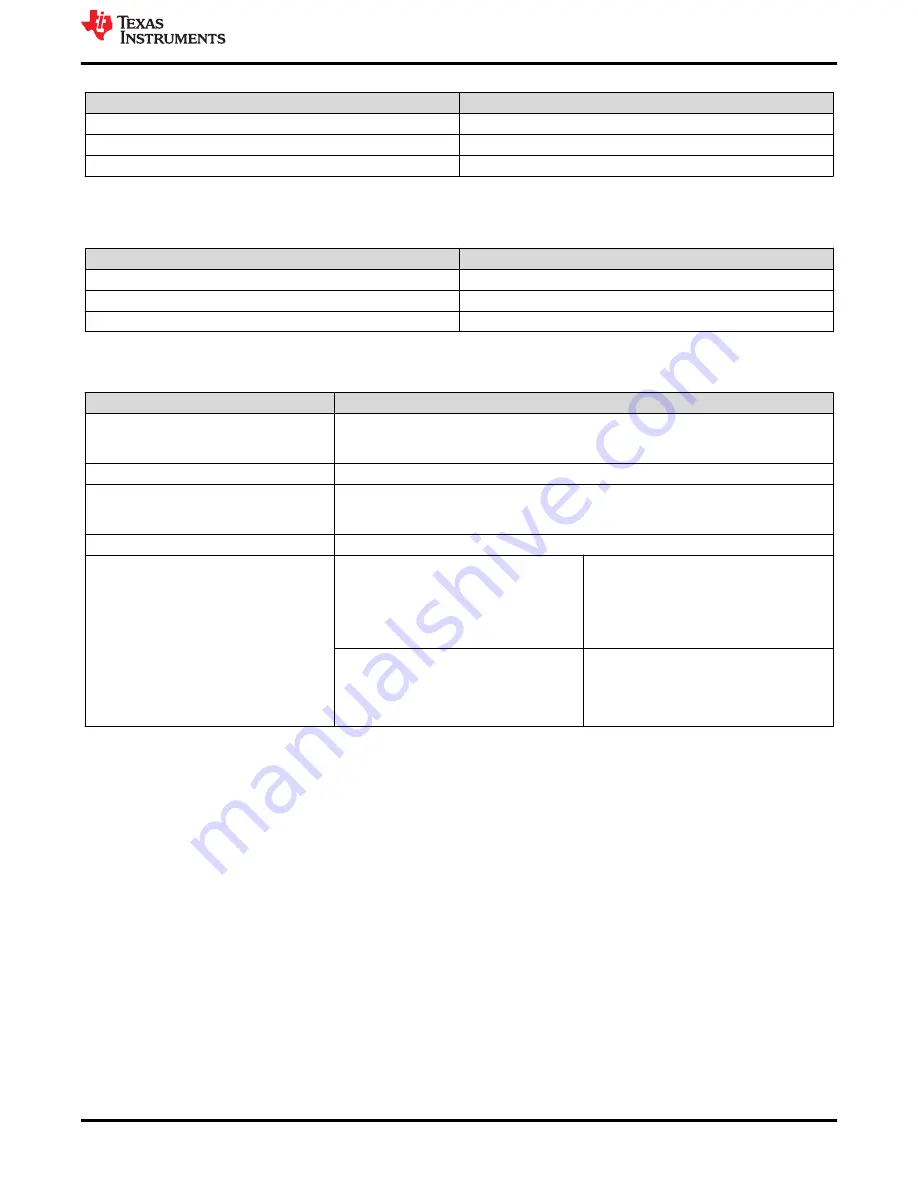

Table 3-5. Header J26, VBACKUP

Configuration

Description

Open

VBACKUP is not connected.

Pin1, Pin2: Closed (Default)

VCCA is connected to the PMIC Battery Backup and VBACKUP.

Pin2, Pin3: Closed

Cell C3 is connected to the PMIC Battery Backup and VBACKUP.

(1)

C3 is not populated on the EVM, but left to the end user to populate with either a coin cell or super cap, depending upon the desired

use case.

Table 3-6. Header J30 VIO_IN Voltage Select

Configuration

Open

Not Allowed, 1.8 V or 3.3 V must be selected.

VIO Select, 3.3 V: Closed (Default)

VIO_IN is 3.3 V.

VIO Select, 1.8 V: Closed

VIO_IN is 1.8 V.

1. In addition to J7 and J26, the lower portion of J15 is also used for the selection of VSYS and GPIO1.

Table 3-7. Header J15, V3V3/VSYS/V5V0, GPIO1/I2C/SPI

Configuration

Description

V3V3, VSYS: Closed (Default)

3.3 V from U13 is connected to VSYS (VCCA). U13 is supplied with the 5 V from the USB

connection (VBUS) through J47. VBUS is not intended to support heavy load conditions of

greater than 3 W. This is the default state of the EVM

VSYS, V5V0, and V3V3: Open

VSYS, VBUS, and USB_3V3 are isolated. VSYS should be powered from J6.

VSYS, V5V0: Closed

5 V from U14 is connected to VSYS (VCCA). U14 is supplied with the 5 V from the USB

connection (VBUS) through J47. VBUS is not intended to support heavy load conditions of

greater than 3 W.

SCL2/CS, GPIO1: Open

GPIO mode. GPIO1 of the PMIC is connected to IO1 of the MCU.

SCL2/CS, GPIO1: Closed (Default)

I2C mode (J7 SPI_EN: Open)

Q&A Watchdog mode. GPIO1 of the PMIC

should be in the Alternative function to

support the Q&A Watchdog and the I2C

mode selected. This setting is done in

conjunction with J7, GPIO2, SDA2/SDO:

Closed

SPI mode (J7 SPI_EN: Closed)

SPI mode, Chip Select. GPIO1 of the PMIC

should be in the Alternative function to

support SPI communication. This setting is

done in conjunction with J7, GPIO2, SDA2/

SDO: Closed

1. The PMIC device can be configured for a power good level of 3.3 V or 5.0 V for the VCCA pin. Align the

V3V3/VSYS/VBUS jumper with the PMIC configuration. The default PMIC configuration is 3.3 V.

3.5 Signal Headers

Signal headers are provided for the LDOs, BUCK regulators, and GPIO signals. Headers J13 (LDOs), J12

(BUCKs), and J11 (GPIOs) are placed on the perimeter of the board to enable probing of these signals even

when in a stacked configuration.

There are 6 signal headers associated with the LDO; five are shown in the EVM silk screen capture,

These include J20 and J21, the power inputs to the LDOs, J14 and J13, the LDO outputs, and J18 and J19

which can be used to measure Power Supply Rejection Ratio (PSRR) on LDO3 and LDO4. All pins of J20 are

connected to the VCCA, and J20 is placed next to J21 to easily connect all the LDO power inputs to the VCCA;

this is the default jumper configuration. An external power supply for the LDOs can also be applied directly to

J21.

EVM Details

SLVUBT0A – JUNE 2020 – REVISED JANUARY 2021

TPS6594x-Q1 Evaluation Module

9

Copyright © 2021 Texas Instruments Incorporated