External Component Selection

2-18

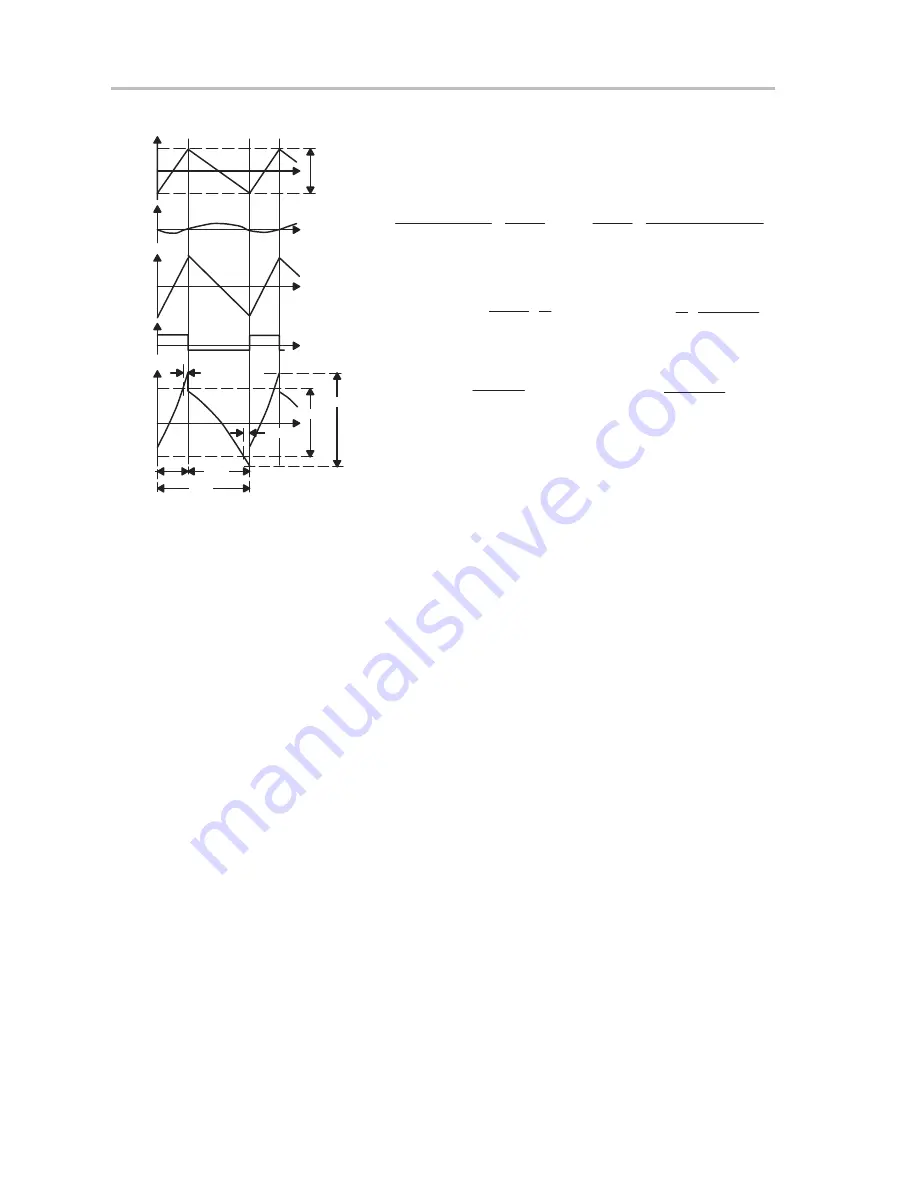

Figure 2–6. Output Ripple Voltage Detail

(a)

Current waveform through output capacitor

(b)

Voltage waveform across ideal capacitor with initial value at

beginning of high-side MOSFET on-time

V

C

+

I

t2

2

Co

D

Ts

–

I

t

2

Co

High-side MOSFET ON

High-side MOSFET OFF

V

C

+

I

t

2

Co

–

I

t2

2

Co

(1–D)

Ts

(c)

Voltage waveform across ESR

V

ESR

+

ESR

I

t

D

Ts

–

I

2

High-side MOSFET ON

High-side MOSFET OFF

V

ESR

+

ESR

I

2

–

I

t

(1

–D)

Ts

(d)

Voltage waveform across ESL

V

ESL

+

ESL

I

D

Ts

High-side MOSFET ON

High-side MOSFET OFF

V

ESL

+

–

ESL

I

(1

–D)

Ts

Hyst

(a)

(b)

(c)

(d)

(e)

IAC

∆Ι

VC

VESR

VESL

Vripple

tdel

t

t

t

t

tdel t

Vp–p

ton

toff

Ts

(e)

Composite output voltage ripple waveform

V

ripple

+

V

C

)

V

ESR

)

V

ESL

Figures 3–6, 3–15, 3–24, and 3–33 show the phase voltage (voltage at

junction of high-side MOSFET with low-side MOSFET), and output voltage

ripple waveforms for the example circuit of Figure 1–3. The output voltage

waveform is slightly different from the theoretical waveform of Figure 2–6(e)

due to the smoothing effect of the 10-

µ

F ceramic capacitor in parallel with the

electrolytic capacitors.

2.2.4.2

Switching Frequency Equation

Assume that the input and output voltage ripple magnitudes are relatively

negligible compared to the dc component. Also assume that the time constant

L/(R

DS(on)

+ R

L

), where L is the output inductance, R

L

is the inductor resistance

and R

DS(on)

is the on-state resistance of the high-side MOSFET(s), is high in

comparison with the switching period. Assume the body diode conduction time

and switching transition time are much smaller than the switching period.

These assumptions are reasonable for low voltage ripple and high efficiency

regulators. In such a case the output inductor current can be modeled as

the sum of the dc component, which is equal to the output current

Io, and

the ac linear ramp component, which flows through the output capacitor

[Figure 2–6(a)].

The numbered equations in this section are used to derive the switching

frequency equation.

Summary of Contents for SLVU013

Page 1: ... June 1999 Mixed Signal Linear Products User s Guide SLVU013 ...

Page 8: ...viii ...

Page 19: ...Board Layout 1 11 Introduction Figure 1 7 Bottom Layer Top VIew Bottom Layer Top View ...

Page 20: ...1 12 ...

Page 46: ...Test Setup 3 6 Figure 3 1 Test Setup 5V Power Supply Load 12 V Power Supply ...