Public Version

PRCM Functional Description

www.ti.com

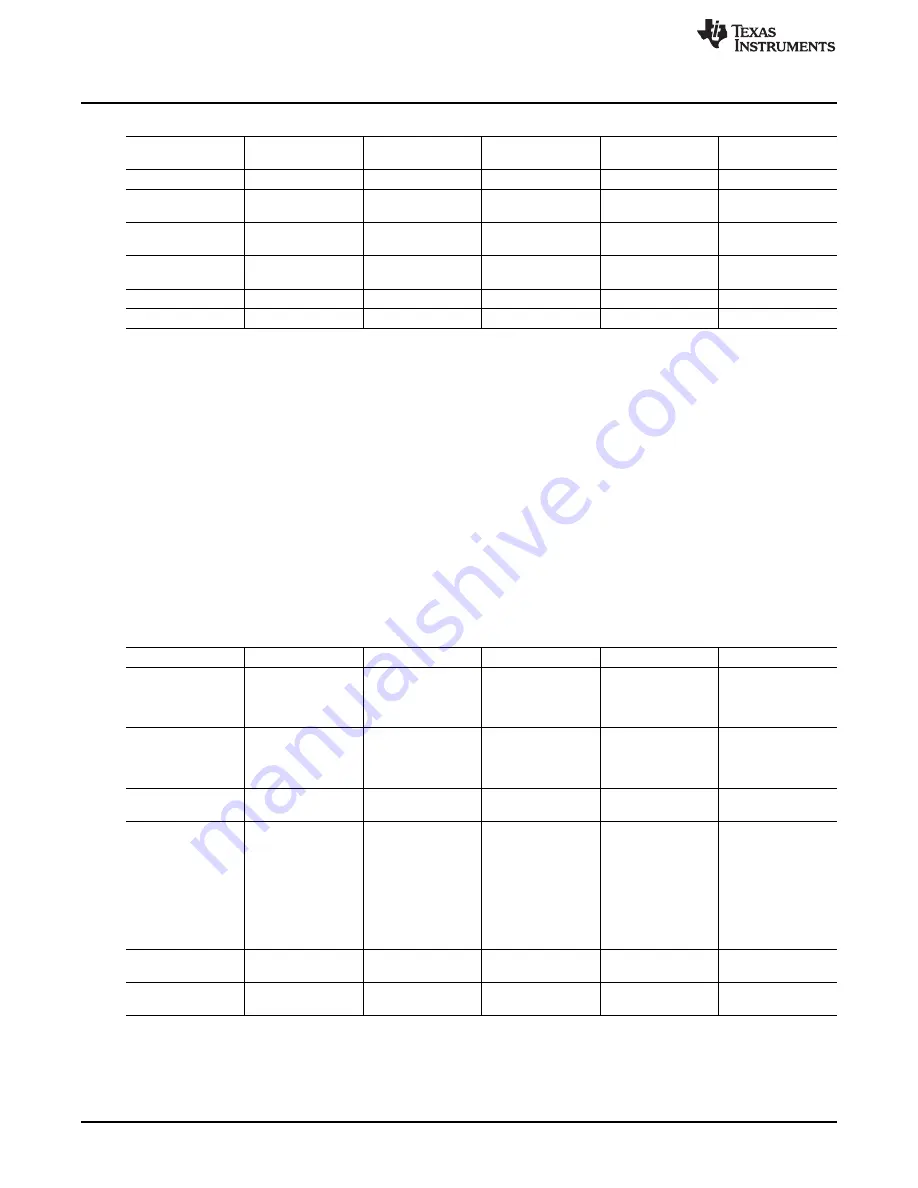

Table 3-39. DPLL Power Modes

Mode

Clock Input

Clock Output

DPLL Power State

Power

Latency

Consumption

Locked

On

Lock frequency

ON

Maximum

N/A

Low-power bypass

On

Bypass frequency

ON

Less than locked

Same as low-power

stop

Fast-relock bypass

On

Bypass frequency

ON

Less than locked

Less than

low-power bypass

Low-power stop

On

Bypass frequency

ON

Less than locked

Same as low-power

bypass

MN bypass

On

Bypass frequency

ON

Less than locked

Maximum

Off

Off

Off

Off

Minimum

Maximum

A DPLL power mode can be achieved on a software request (manual) and/or automatically (automatic),

depending on the specific hardware conditions. After a device power-on reset, the DPLL can be kept in

low-power stop mode (DPLL2 , DPLL4, and DPLL5) or MN bypass mode (DPLL1 and DPLL3).

A DPLL can switch from one mode to the other as a result of the following:

•

Software-programmed transition only (manual): The software configures a dedicated register for the

next desired DPLL mode. It must ensure that the transition can be performed based on the activity on

the device.

•

Combined software-programmed and hardware-conditions-based transition (automatic): The PRCM

module triggers the transition when the software requests it (by configuring the registers) and the

hardware conditions are satisfied. When the hardware conditions are no longer met, the PRCM module

triggers the return transition.

For automatic transition, automatic mode must be enabled by programming the

PRCM.

or the PRCM.

_<processor_name> registers.

describes the manual and automatic control of the DPLL power modes by the PRCM module.

Table 3-40. DPLL Power Mode Support

Mode

DPLL1

DPLL2

DPLL3

DPLL4

DPLL5

Locked

Software request

Software request

Software request

Software request

Software request

(manual) or MPU

(manual) or IVA2.2

(manual) or CORE

(manual) or at least

(manual) or at least

wakes up

wakes up

wakes up

one peripheral clock one peripheral clock

(automatic).

(automatic).

(automatic).

is used (automatic).

is used (automatic).

Low-power bypass

Software request

Software request

Software request

N/A

N/A

(manual)

(manual)

(manual) or all

interface clocks are

gated (automatic).

Fast-relock bypass

N/A

N/A

Software request

N/A

N/A

(manual)

Low-power stop

MPU is idle

Software request

Device is idle

(Default state)

(Default state)

(automatic).

(manual) or IVA2.2

(automatic).

Software request

Software request

is idle (automatic) or

(manual) or all

(manual) or all

on global reset

functional clocks

functional clocks

release (automatic).

from DPLL are

from DPLL

unused or on global

(120-MHz clock) are

reset release

unused or on global

(automatic).

reset release

(automatic).

MN bypass

Global reset

N/A

Global reset

N/A

N/A

(automatic)

(automatic)

Off

Device off

Device off

Device off

Device off

Device off

(automatic)

(automatic)

(automatic)

(automatic)

(automatic)

330

Power, Reset, and Clock Management

SWPU177N – December 2009 – Revised November 2010

Copyright © 2009–2010, Texas Instruments Incorporated