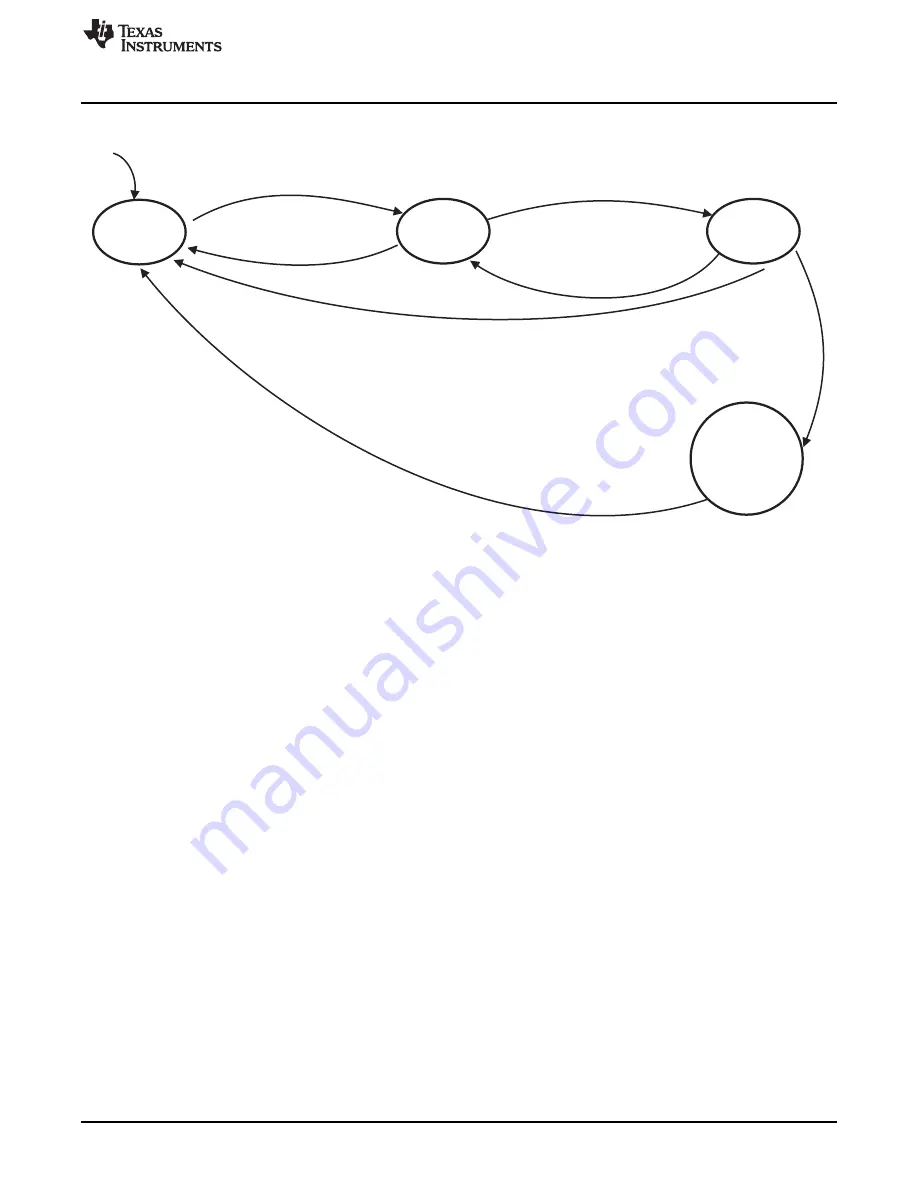

Timer started

Timer loaded

DSI_TIMING1[31] TA_TO = 0x0

by software

DSI_TIMING1[31] TA_TO = 0x1

RESET

DSI_TIMING1[31] TA_TO = 0x0 by software

PPI TurnRequest signal

asserted by DSI protocol

engine

Time-out

IDLE

DSI_TIMING1[31] TA_TO = 0x0 by hardware

BTA accepted by peripheral

TA_TO

interrupt

generation and

ForceTxStopMode

sequence

dss-173

Public Version

www.ti.com

Display Subsystem Functional Description

Figure 7-97. TurnRequest FSM

The DSI protocol engine asserts TurnRequest signal during one TxClkEsc cycle when the turn-around is

enabled through the DSS.

[6] BTA_EN bit (for more information, see

, Bus

Turnaround). The DSS.

[31] TA_TO bit is set/reset by software to respectively enable/disable

the timer for turnaround procedure failure. It can be reset by software or automatically by hardware when

the time out occurs.

The timer is loaded with the value in number of DSI_FCLK cycles:

[28:16] TA_TO_COUNTER x ((

[30] TA_TO_X16 x 15) + 1) x

((

[29] TA_TO_X8 x 7) + 1).

When the TA_TO_IRQ interrupt is generated (turn-around timer expired, and procedure failed), the

hardware automatically asserts ForceTXStopMode in order for the DSI_PHY to drive LP-11 stop state.

The ForceTXStopMode timer is used to define the minimum duration of LP-11 state. The Stop State can

be longer if there is no activity.

The hardware resets the ForceTXStopMode bit, followed by an internal logic reset except all register

values and TX FIFO content, then resets the DSS.

[0] IF_EN bit. The software should take

action to recover by resetting the peripheral, for example, if it is not responding. It should wait for

DSS.

[15] FORCE_TX_STOP_MODE_IO and DSS.

[0] IF_EN bits to be reset to 0

before starting the recovery sequence.

7.4.3.7.4 Peripheral Reset Timer

The peripheral reset timer is not implemented in the DSI protocol engine module. Such as the Twakeup

timer, a general-purpose timer (GPTimer)should be used in case of reset of the peripheral to determine

when the peripheral is ready again for operation.

7.4.3.7.5 HS TX Timer

The HS TX timer is used to detect when the host has been in TX mode for too long. When time-out

occurs, the EOT is forced. The timer is reloaded when a start of high speed transmission occurs. It is

enabled/disabled by software through the DSS.

[31] HS_TX_TO bit. The interrupt

HS_TX_TO_IRQ is generated when the timer expires. The DSS.

[14] HS_TX_TO_IRQ

bit is set to 1 when the HS TX time-out occurs.

1677

SWPU177N – December 2009 – Revised November 2010

Display Subsystem

Copyright © 2009–2010, Texas Instruments Incorporated