Public Version

www.ti.com

Camera ISP Basic Programming Model

•

width 4096 (if vertical resize value is in range: (

[19:10] VRSZ + 1) = [64..512])

•

width 2048 (if vertical resize value is in range: (

[19:10] VRSZ + 1) = [513..1024])

–

Must be even

–

Must be a multiple of 16 bytes (for vertical upsizing)

•

When input is from preview engine/CCDC:

–

The input height and width must be <= the output of the preview engine/CCDC.

–

The input address and offset must be zero.

–

The input cannot be color-separated data.

•

If the source is memory:

–

The vertical start pixel must be zero.

–

The horizontal start pixel must be within the range: 0:15 for color interleaved, 0:31 for color

separate data.

–

The memory output line offset and address must be on 32-byte boundaries.

•

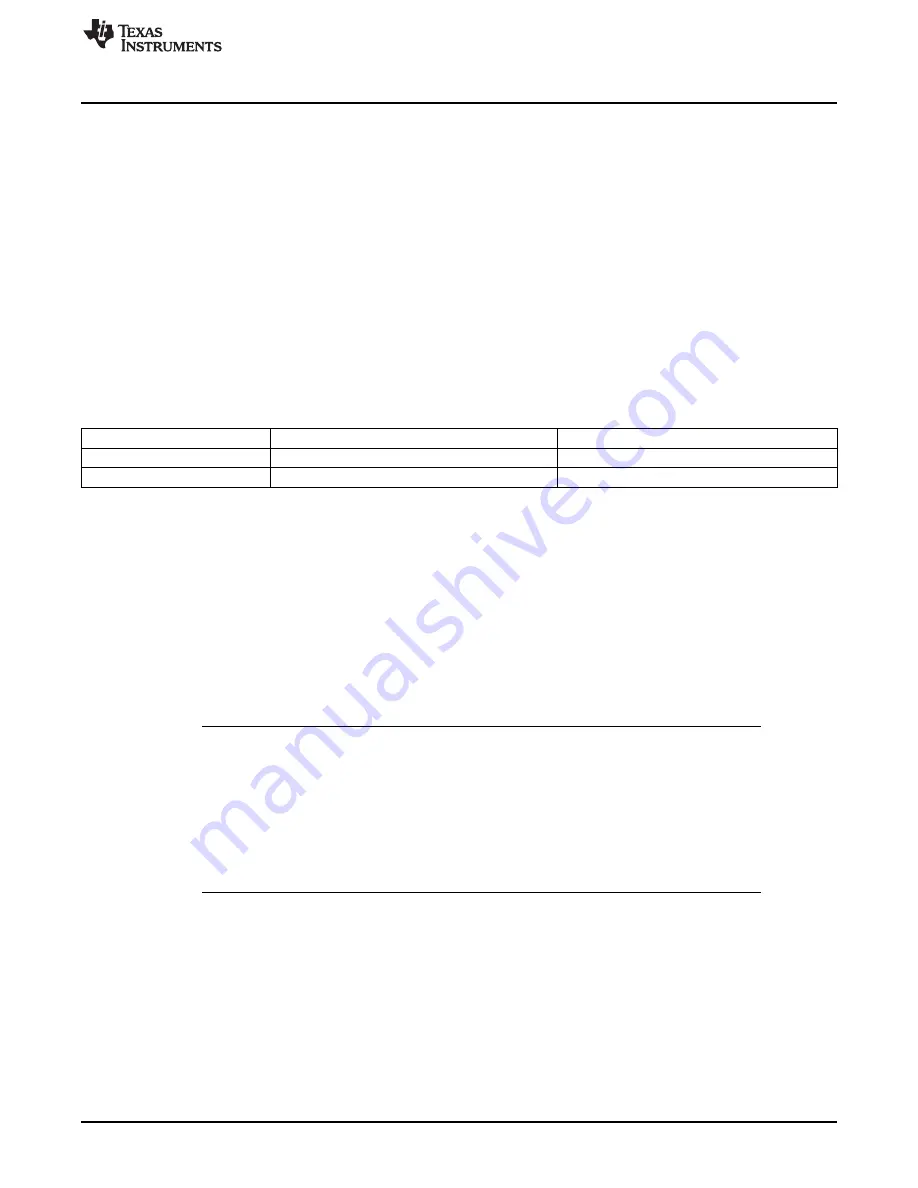

Input height and width MUST adhere to the equations in

Table 6-71. Camera ISP Resizer How to Set Input Height and Width

8-phase, 4-tap mode

4-phase, 7-tap mode

[12:0] HORZ

(32*sph + (ow - 1)*hrsz + 16) >> 8 + 7

(64*sph + (ow - 1)*hrsz + 32) >> 8 + 7

[28:16] VERT

(32*spv + (oh - 1)*vrsz + 16) >> 8 + 4

(64*spv + (oh - 1)*vrsz + 32) >> 8 + 7

Where:

- sph = Start phase horizontal (

[22:20] HSTPH)

- spv = Start phase vertical (

[25:23] VSTPH)

- ow = Output width (

[11:0] HORZ + extra)

- oh = Output height (

[27:16] VERT)

- hrsz = Horizontal resize value (

[9:0] HRSZ + 1)

- vrsz = Vertical resize value (

[19:10] VRSZ +1)

extra = 0 when

[17:16] ALGO = 0 (edge enhancement disabled)

extra = 4 when

[17:16] ALGO != 0 (edge enhancement enabled)

NOTE:

Normally, (for example, for a QVGA display or encoded PAL video), the output size, not the

input size, matters. The image provided by preview/CCDC/memory must have an adequate

output size: at least

[12:0] HORZ x

[28:16] VERT. If the image is

bigger, the resizer can crop extra pixels.

The phase is usually computed to keep the center of the image at the same location. This

permits a natural-looking continuous digital zoom.

For this reason,

explains how to compute

[12:0] HORZ ,

[28:16] VERT, not how to compute the output size.

6.5.9 Programming the H3A

This section discusses issues related to software control of the H3A module. It lists which registers are

required to be programmed in different modes, how to enable and disable the H3A, and how to check the

status of the H3A. It also discusses the different register access types and enumerates programming

constraints.

6.5.9.1

Camera ISP H3A Setup/Initialization

This section discusses the configuration of the H3A required before image processing can begin.

1289

SWPU177N – December 2009 – Revised November 2010

Camera Image Signal Processor

Copyright © 2009–2010, Texas Instruments Incorporated