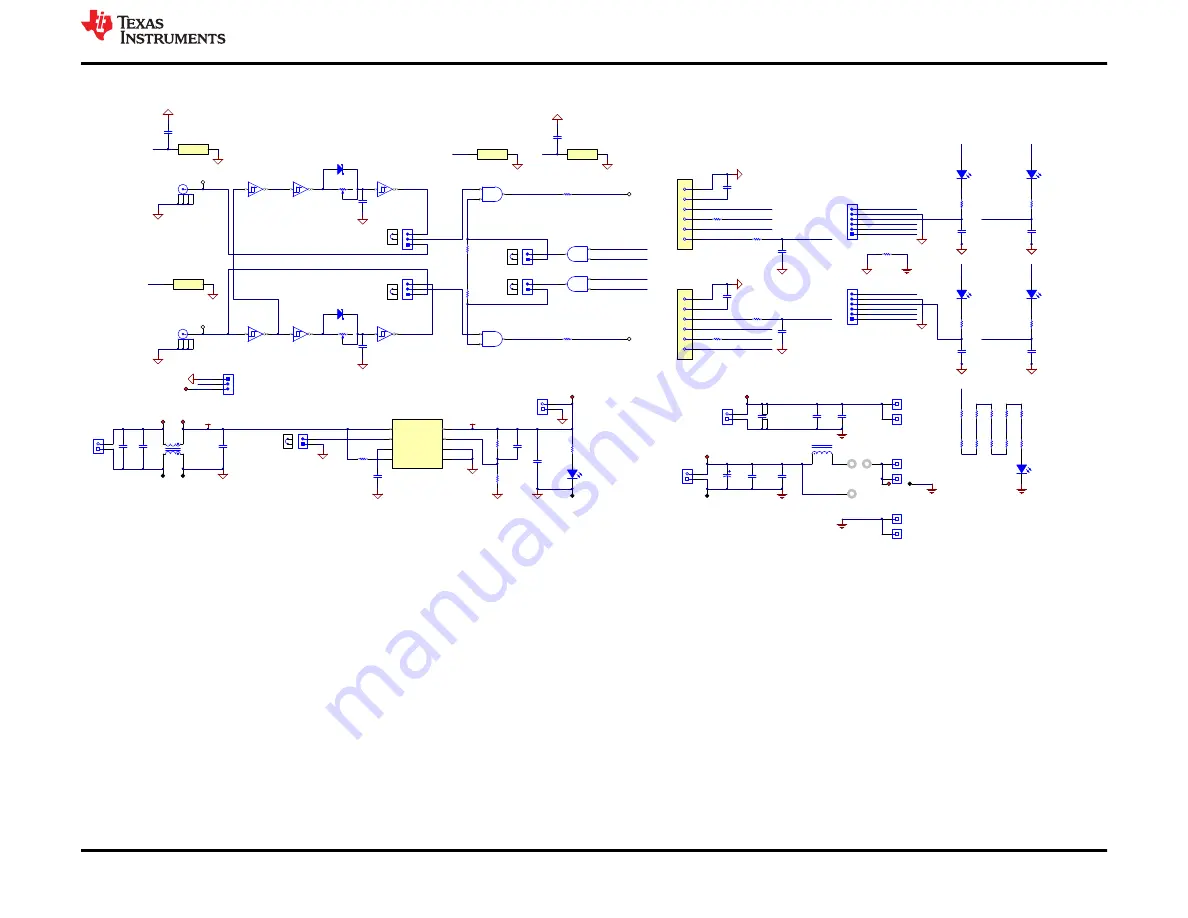

4 Mother Board Schematic

AGND

AGND

AGND

AGND

Vin

HS_FET_PWM

LS_FET_PWM

PGND

VAUX 12V

AGND

PGND

PGND

PGND

PGND

AGND

12V

AGND

VIN

1

EN

3

SS

5

GND

4

FB

6

RON

2

VOUT

7

EP

8

LMZ12001EXTTZ/NOPB

U4

AGND

AGND

AGND

AGND

630V

0.1uF

CIN3

630V

0.1uF

CIN4

1

2

3

4

5

J3

112404

1

2

3

4

5

J8

112404

D1

BAT54WS-7-F

7

1

S

N

7

4

LV

C

3

G

1

4D

C

U

TG

4

U3A

5

3

S

N

7

4

LV

C

3

G

1

4D

C

U

TG

4

U3B

2

6

S

N

7

4

LV

C

3

G

1

4D

C

U

TG

4

U3C

GND

4

VCC

8

SN74LVC3G14DCUTG4

U3D

D3

BAT54WS-7-F

5

3

S

N

7

4

LV

C

3

G

1

4D

C

U

TG

4

U5B

2

6

S

N

7

4

LV

C

3

G

1

4D

C

U

TG

4

U5C

7

1

S

N

7

4

LV

C

3

G

1

4D

C

U

TG

4

U5A

AGND

GND

4

VCC

8

SN74LVC3G14DCUTG4

U5D

7

1

2

U1A

3

5

6

U1B

VCC

8

GND

4

U1C

AGND

1

3

5

7

9

11

J5A

HLE-106-02-G-DV-BE-A

2

4

6

8

10

12

J5B

HLE-106-02-G-DV-BE-A

1

2

J6

282834-2

630V

0.1uF

COUT3

630V

0.1uF

COUT4

0

R9

1

2

3

J7

TSW-103-07-G-S

SH-J1

SNT-100-BK-G

1.6k

R31

Green

1

2

5V_EN

LG L29K-G2J1-24-Z

1

2

3

4

47uH

47uH

L3

HS_FET_PWM

HS_FET_OCZ

HS_FET_TEMP

HS_FET_FAULTZ

AGND

LS_FET_PWM

LS_FET_OCZ

LS_FET_TEMP

LS_FET_FAULTZ

1.18k

R26

AGND

PGND

30k

R16

30k

R17

30k

R11

30k

R12

30k

R18

30k

R13

30k

R19

30k

R14

30k

R20

30k

R10

H

V

B

U

S

Red

1

2

HS_FLT

LS L29K-G1J2-1-Z

5

4

1

2

3

6

J2

TSW-106-07-G-S

5

4

1

2

3

6

J4

TSW-106-07-G-S

12V

VAUX

ACMGND

AGND2

AGND1

HVIN

HVOUT

PGND4

SW

PGND5

PWM_HS

PWM_LS

HS_FET_PWM

LS_FET_PWM

5

V

5V

5V

5V

5V

LS_FET_FAULTZ

SH-J2

SNT-100-BK-G

SH-J3

SNT-100-BK-G

LS_FET_TEMP_FILT

HS_FET_TEMP_FILT

3

5

6

U2B

VCC

8

GND

4

U2C

AGND

AGND

5V

AGND

AGND

Red

1

2

LS_FLT

LS L29K-G1J2-1-Z

5

V

AGND

AGND

5K

R3

3224X-1-502E

5K

R15

3224X-1-502E

5V

1

2

J12

282834-2

AGND

5V

AGND

25V

10uF

C15

6.3V

100uF

C17

22nF

50V

C16

33.2k

R28

22nF

50V

C20

AGND

600V

150uF

C25

3.3k

R1

3.3k

R5

LS_FET_OCZ

HS_FET_OCZ

7

1

2

U2A

HS_FET_FAULTZ

1

2

3

J14

TSW-103-07-G-S

SH-J5

SNT-100-BK-G

J17

3267

J16

3267

J18

3267

1

2

J10

TSW-102-07-G-S

1

2

J11

TSW-102-07-G-S

5

V

100k

R6

100k

R22

3

1

2

4

900V

20µF

C22

Yellow

1

2

HS_OC

SML-E12Y8WT86

5

V

AGND

AGND

3.3k

R29

HS_FET_OCZ

Yellow

1

2

LS_OC

SML-E12Y8WT86

5

V

AGND

AGND

3.3k

R30

LS_FET_OCZ

0

R2

0

R4

Green

1

2

HVIN_EN

LG L29K-G2J1-24-Z

VAUX

HVBUS

HVOUT

PWM_HS

PWM_LS

PGND

S

W

L2

12

V

au

x

1µF

25V

C1

1µF

25V

C9

1µF

25V

C18

50V

39pF

C10

50V

39pF

C23

50V

39pF

C12

50V

39pF

C5

50V

39pF

C14

50V

39pF

C21

25V

10uF

C19

1

2

J1

0395443002

1

2

J9

0395443002

1

HVBUS1

1

SW1

1

PGND1

1

HVBUS2

1

SW2

1

PGND2

SH-J4

SNT-100-BK-G

1

2

J13

TSW-102-07-G-S

6.20k

R25

HS_FET_TEMP

AGND

HS_FET_TEMP_FILT

105k

R8

50V

1600pF

C2

HS_FET_OCZ

100

R7

HS_FET_FAULTZ

HS_FET_PWM

5V

AGND

1µF

25V

C8

12V

AGND

1µF

25V

C6

LS_FET_TEMP

AGND

LS_FET_TEMP_FILT

105k

R27

50V

1600pF

C3

LS_FET_OCZ

100

R21

LS_FET_FAULTZ

LS_FET_PWM

1

2

3

J15

TSW-103-07-G-S

AGND

12V

TACH

TACH

Figure 4-1. LMG342X-BB-EVM Schematic

LMG352XEVM-04X Schematic

SNOU178A – OCTOBER 2020 – REVISED FEBRUARY 2021

LMG352XEVM-04X User Guide

11

Copyright © 2021 Texas Instruments Incorporated