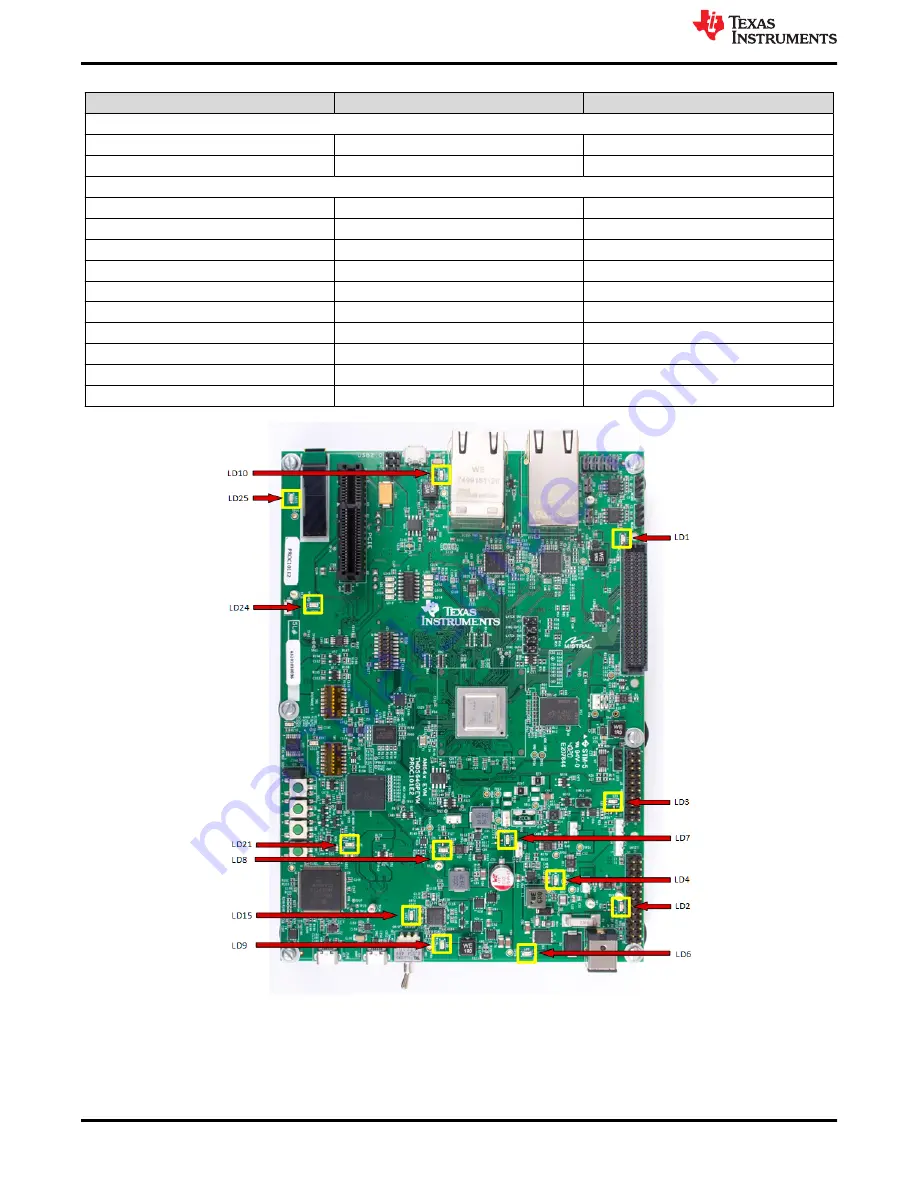

Table 3-5. Power LEDs

Sl.No

Power Supply

LED REF

Before SW1 TURN ON

1

VMAIN

LD6

2

VCC3V3_TA

LD24

After SW1 TURN ON

3

VCC_5V0

LD15

4

VCC3V3_PREREG

LD4

5

VCC_3V3_SYS

LD9

6

VDD_2V5

LD1

7

VDD_1V1

LD10

8

VDDA1V8

LD8

9

VDD_CORE

LD2

10

VCC_CORE

LD7

11

VDD_2V8

LD25

12

VCC1V2_DDR

LD3

Figure 3-6. Power Good LEDs

System Description

14

AM64x GP EVM User's Guide

SPRUIX0B – FEBRUARY 2021 – REVISED MARCH 2021

Copyright © 2021 Texas Instruments Incorporated