TS-3200 User’s Manual

Technologic Systems

05/21/2009

13

1) Write to the upper 16 bits (WDTRLDH at 0F4C0h) of the reload value (the number of clock cycles

before the watchdog timer times out) followed by a write to the lower 16 bits (WDTRLDL at

0F4C2h) of the reload value.

2) Perform a

Watch Dog Feed

. Write 2 sequential words: 0F01Eh followed by 0FE1h to the watchdog

timer clear register (WDTCLR). The WDTCLR is located at 0F4C8h.

3) Software must periodically perform step two (the Watch Dog Feed) before the watchdog timer

times out to prevent a system reset.

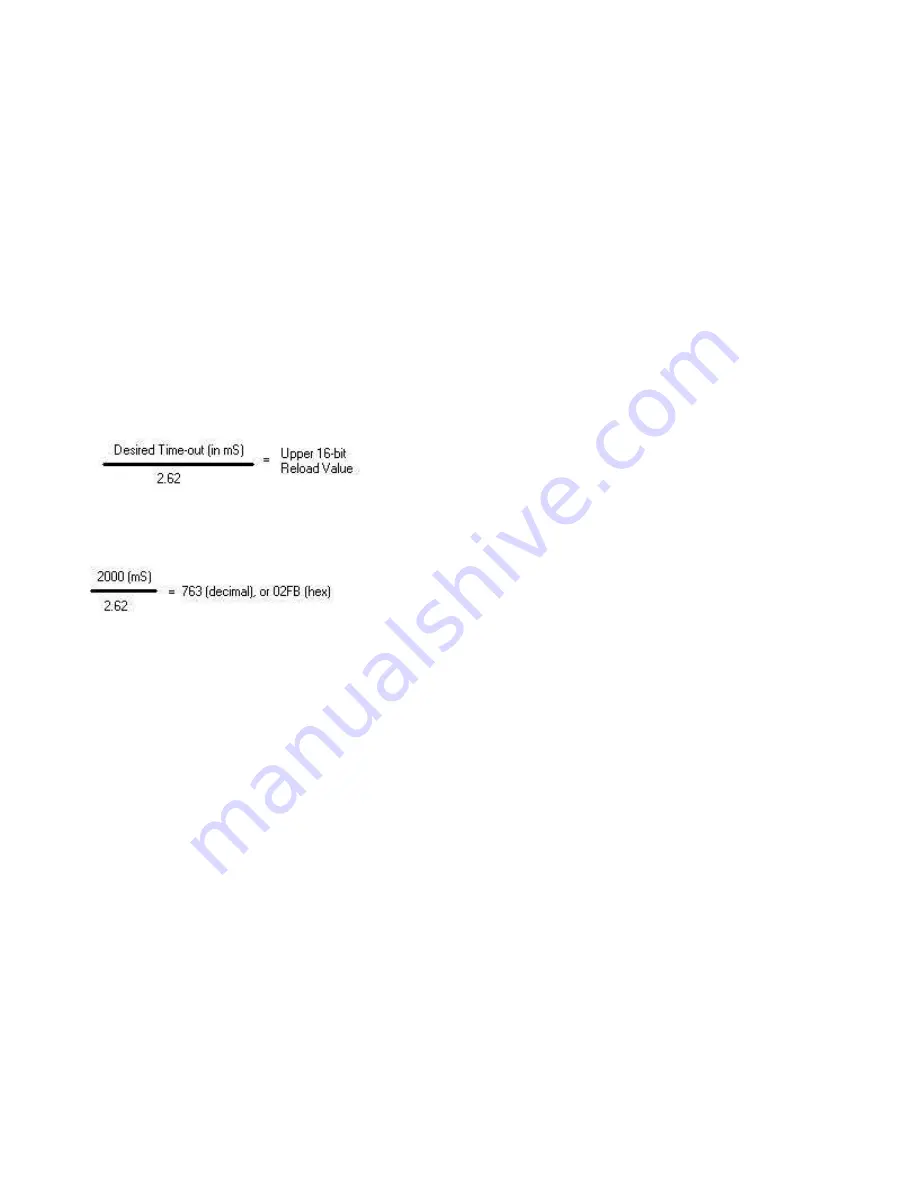

Each increment in the value of the upper 16-bits (WDTRDH) of 32-bit Reload Register adds 2.62 mS to

the Watch Dog Timeout Value. The lower 16 bits (WDTRDL) are insignificant and can be loaded with

zero. This fact allows the following simple method of calculating a “Reload Constant” (assuming a

25MHz 386EX clock):

For example: if a 2 second time-out is desired, then

So WDTRLDH = 02FBh and WDTRLDL = 0000

When the WDT times out, it causes a complete hardware reset to the entire TS-3200 and also asserts

RESETDRV on the PC/104 Bus.

The following code illustrates using the WDT to implement a software reset routine. The WDT is

initialized with a very low “Reload Constant”.

Void main ()

{

const int WDTCLR = 0xF4C8;

const int WDTRLDH = 0xF4C0;

const int WDTRLDL = 0xF4C2;

int n = 0;

outport(WDTRLDH, 0x0001); // Reload Constant = 2.6 mS

outport(WDTRLDL, 0x0000); //

outport(WDTCLR, 0xF01E); // Watch Dog Feed word 1

outport(WDTCLR, 0x0FE1); // Watch Dog Feed word 2

for (n =0; n = 1; )

{ //endless loop…system will

//be reset in about 2.62 milliseconds anyway

Summary of Contents for TS-3200

Page 1: ...TS 3200 User s Manual...