1

2

3

4

5

6

A

B

C

D

6

5

4

3

2

1

D

C

B

A

Title

Number

Revision

Size

Orcad C

Date:

10-Jun-2004

Sheet of

File:

C:\DOCUME~1\ADMINI~1\LOCALS~1\Temp\Rar\NEW SKY5020.DDB

Drawn By:

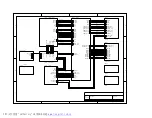

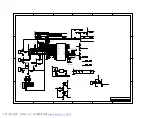

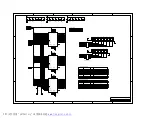

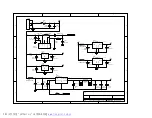

FSDATA5

FSDATA47

FSDATA42

FSDATA9

FSDATA45

FSDATA2

FSDATA40

FSDATA22

FSADDR7

FSDATA15

FSDATA4

FSDATA21

FSDATA34

FSDATA31

FSDATA18

FSDATA44

FSDATA30

FSDATA19

FSDATA16

FSDATA7

FSDATA0

FSDATA28

FSDATA8

FSDATA32

FSDATA20

FSDATA3

FSDATA1

FSDATA6

FSDATA24

FSDATA39

FSDATA41

FSDATA12

FSDATA27

FSDATA33

FSDATA29

FSDATA46

FSDATA43

FSDATA35

FSDATA11

FSDATA10

FSDATA17

FSDATA37

FSDATA14

FSDATA26

FSDATA38

FSDATA13

FSDATA36

FSDATA25

FSDATA23

FSADDR1

FSADDR6

FSADDR0

FSADDR5

FSADDR2

FSADDR3

FSADDR4

FSADDR0

FSADDR2

FSADDR6

FSADDR1

FSADDR11

FSADDR7

FSADDR4

FSADDR8

FSADDR10

FSADDR5

FSADDR9

FSADDR8

FSADDR5

FSADDR8

FSADDR6

FSADDR11

FSADDR2

FSADDR8

FSADDR1

FSADDR0

FSADDR9

FSADDR2

FSADDR13

FSADDR6

FSADDR0

FSADDR9

FSADDR10

FSADDR4

FSADDR9

FSADDR1

FSADDR11

FSADDR7

FSADDR11

FSADDR10

FSADDR3

FSADDR5

FSADDR12

FSADDR3

FSADDR3

FSADDR7

FSADDR4

FSADDR10

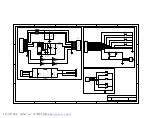

2

3

1

JP809

C819

220P

2

3

1

JP813

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

RN800

10K

2

3

1

JP806

C815

0.1uF

C803

0.1uF

2

3

1

JP805

2

3

1

JP804

C802

0.1uF

DQ2

5

DQ3

6

DQ4

8

DQ5

9

DQ6

11

DQ1

3

DQ7

12

DQ10

42

DQ8

39

DQ9

40

A0

21

LDQM

14

/WE

15

V

S

S

2

6

V

C

C

1

V

C

C

2

5

V

C

C

Q

7

V

C

C

Q

1

3

DQ0

2

DQ15

49

DQ14

48

DQ12

45

DQ11

43

A1

22

A2

23

A3

24

A4

27

A5

28

A6

29

A8

31

A7

30

A9

32

A10

20

A11

19

/CAS

16

/RAS

17

/CS

18

CKE

34

UDQM

36

V

C

C

Q

3

8

V

C

C

Q

4

4

V

S

S

5

0

V

S

S

Q

4

V

S

S

Q

1

0

V

S

S

Q

4

1

V

S

S

Q

4

7

CLK

35

NC

37

DQ13

46

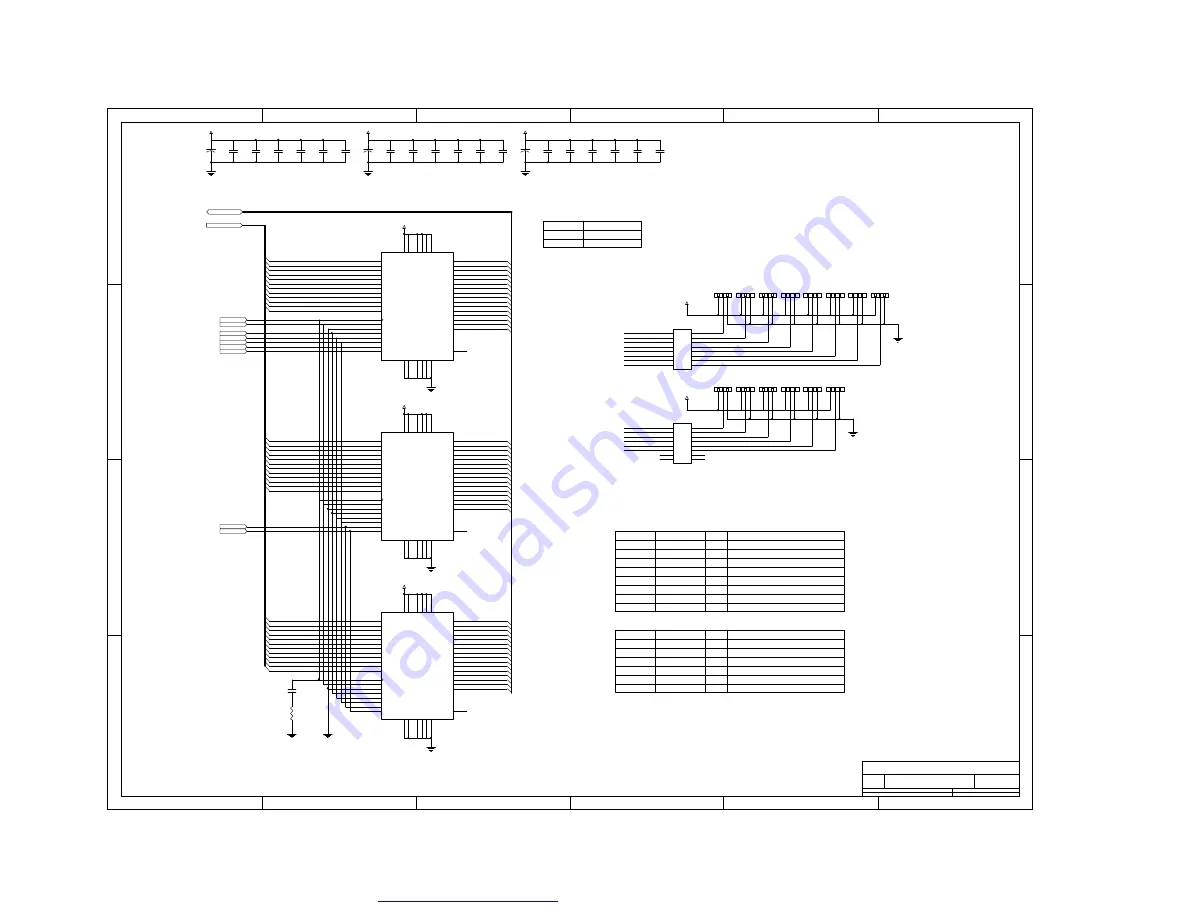

IC800

K4S161622

2

3

1

JP812

C805

220P

C817

0.1uF

2

3

1

JP811

C821

47pF

2

3

1

JP807

C807

22uF/10V

2

3

1

JP810

DQ2

5

DQ3

6

DQ4

8

DQ5

9

DQ6

11

DQ1

3

DQ7

12

DQ10

42

DQ8

39

DQ9

40

A0

21

LDQM

14

/WE

15

V

S

S

2

6

V

C

C

1

V

C

C

2

5

V

C

C

Q

7

V

C

C

Q

1

3

DQ0

2

DQ15

49

DQ14

48

DQ12

45

DQ11

43

A1

22

A2

23

A3

24

A4

27

A5

28

A6

29

A8

31

A7

30

A9

32

A10

20

A11

19

/CAS

16

/RAS

17

/CS

18

CKE

34

UDQM

36

V

C

C

Q

3

8

V

C

C

Q

4

4

V

S

S

5

0

V

S

S

Q

4

V

S

S

Q

1

0

V

S

S

Q

4

1

V

S

S

Q

4

7

CLK

35

NC

37

DQ13

46

IC801

K4S161622

DQ2

5

DQ3

6

DQ4

8

DQ5

9

DQ6

11

DQ1

3

DQ7

12

DQ10

42

DQ8

39

DQ9

40

A0

21

LDQM

14

/WE

15

V

S

S

2

6

V

C

C

1

V

C

C

2

5

V

C

C

Q

7

V

C

C

Q

1

3

DQ0

2

DQ15

49

DQ14

48

DQ12

45

DQ11

43

A1

22

A2

23

A3

24

A4

27

A5

28

A6

29

A8

31

A7

30

A9

32

A10

20

A11

19

/CAS

16

/RAS

17

/CS

18

CKE

34

UDQM

36

V

C

C

Q

3

8

V

C

C

Q

4

4

V

S

S

5

0

V

S

S

Q

4

V

S

S

Q

1

0

V

S

S

Q

4

1

V

S

S

Q

4

7

CLK

35

NC

37

DQ13

46

IC802

K4S161622

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

RN801

10K

C811

220P

C818

220P

C809

0.1uF

2

3

1

JP803

C800

22uF/10V

C801

0.1uF

C813

220P

C816

0.1uF

2

3

1

JP802

C820

220P

C814

22uF/10V

1

2

R800

75

C808

0.1uF

2

3

1

JP801

C810

0.1uF

C812

220P

C804

220P

2

3

1

JP800

C806

220P

2

3

1

JP808

FSDATA[0..47]

FSADDR[0..13]

FSDQM0

FSDQM1

FSDQM2

FSDQM3

FSRAS

FSCLK

FSCKE

FSCAS

FSWE

DVDD_3.3

DVDD_3.3

DVDD_3.3

DVDD_3.3

DVDD_3.3

DVDD_3.3

DVDD_3.3

DVDD_3.3

PLACE RN CLOSE TO MEMORY ICs

SXGA 85Hz

Devices

Input Format

SDRAM SELECTION

2 @ 1M x 16 SDRAM

XGA 85Hz

3 @ 1M x 16 SDRAM

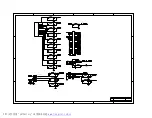

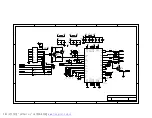

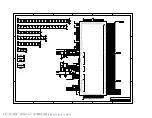

FSADDR11

Pull High ( Six Wires )

OCM_EXTCLK

DESCRIPTION

OCM_CLK

FSADDR(4:0)

x

-

USER_BITS(7:5)

IIC Chip Address

HOST_PROTOCOL

OCM_START

FSADDR6

Pull Low

FSADDR12

FSADDR13

Pull Low

0

FSADDR11

ADDRESS

Pull Low

Pull Low

0

x

FSADDR(10:8)

1

x

ADDR(6:0)

MCU Clock Select ( Default = 0 for RCLK/2 )

NAME

OCM_EXTCLK

Pull Low ( Two Wires )

Status Register ( Can be Used as Panel Selection )

0

FSADDR(10:8)

FSADDR12

Reserved

FSADDR(7)

Status Register ( Can be Used as Panel Selection )

MCU Clock Select ( Default = 0 for RCLK/2 )

Reserved

OCM_CLK

SET

MCU Clock Select ( Default = 0 for INTCLK )

0

FSADDR(6:0)

0

FSADDR13

HOST_PROTOCOL

FSADDR5

USER_BITS(7:5)

ADDRESS

NAME

0

0

0

Status Register ( Can be Used as Panel Selection )

SET

DESCRIPTION

USER_BITS(4:0)

FSADDR(7)

OCM_START

MCU Clock Select ( Default = 0 for INTCLK )

0

TWO-WIRE HOST INTERFACE SETTING

SIX-WIRE HOST INTERFACE SETTING

文件使用

"pdfFactory"

试用版本创建

Summary of Contents for 8T83

Page 3: ...TECHNICAL SPECIFICATION 3 Frequency L L CUSTOM SOFT STANDARD RICH LATIN GREEK...

Page 4: ...TECHNICAL SPECIFICATION 4...

Page 5: ...Chassis Block Diagram 5...

Page 7: ...IC2 MULTI STANDARD VIDEO IF TDA4470 IC602 POWER STR G6653 IC Block Diagram 7...

Page 10: ......

Page 11: ......

Page 12: ...AV IN OUT PC IN PCB Top Layer 12...

Page 13: ...13 AV IN OUT PC IN PCB BOTTOM Layer...

Page 14: ...14 VGA CONTROL PCB Top Layer VGA PCB TOP LAYER CONTROL PCB TOP LAYER...

Page 15: ...Service Adjustments 15...

Page 16: ...Service Adjustments 16...