XAV-AX210

XAV-AX210

40

Sony CONFIDENTIAL

For Authorized Servicer

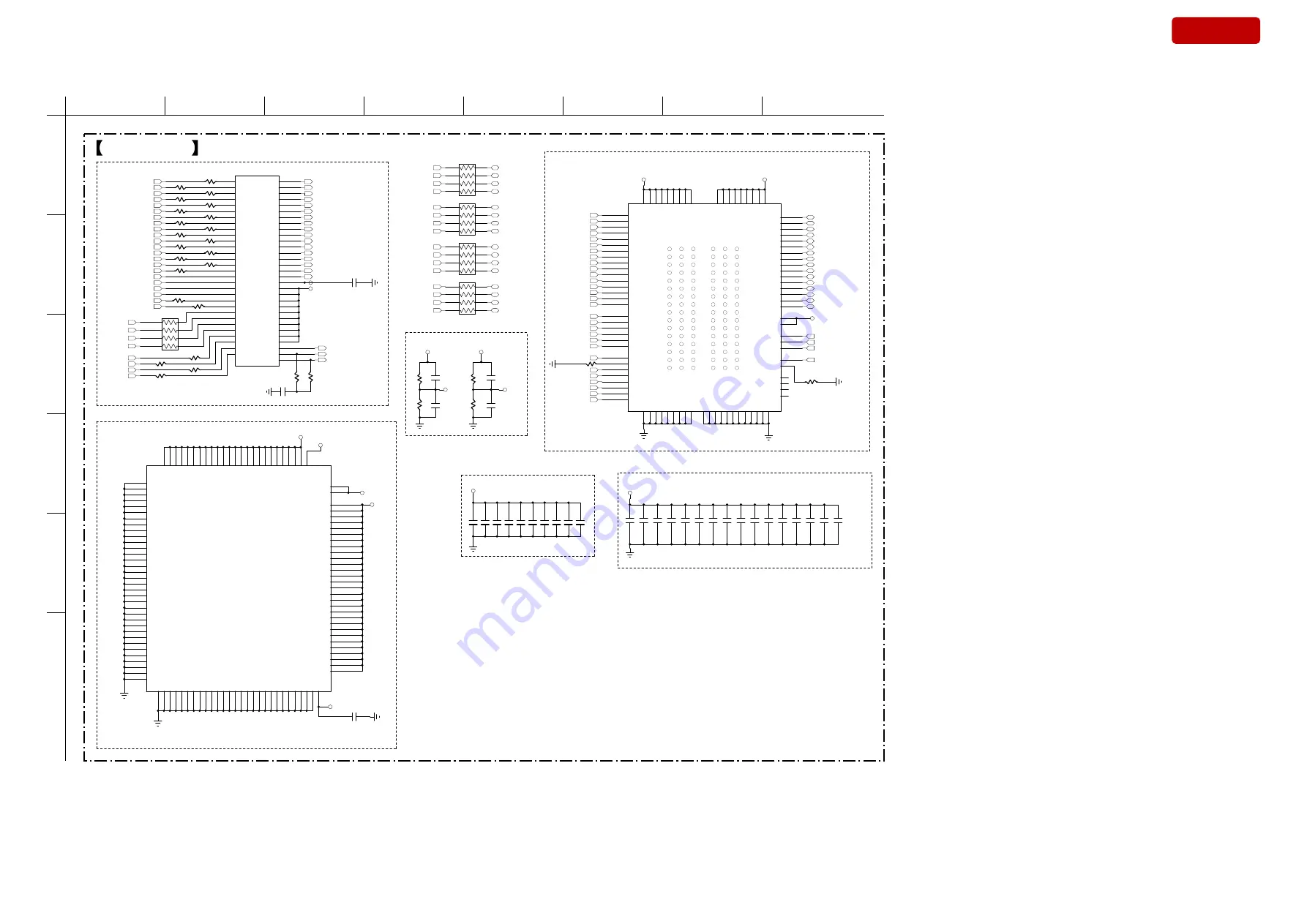

5-18. SCHEMATIC DIAGRAM - TFT Board (4/8) -

A

E

D

B

C

1

2

3

4

5

6

7

8

(4/8)

TFT BOARD

F

Power bypass cap. for VDDQ_15

Power bypass cap. for VDDQ_15

NOM. 2Gb

MAX. 4Gb

1. NT5CB128M16FP-DI -40°C~95°C

5&

R25

75R

R24

75R

C26

10pF

W8

A_A0

Y6

A_A1

M3

A_A2

T3

A_A3

V4

A_A4

R4

A_A5

W4

A_A6

P4

A_A7

Y3

A_A8

M4

A_A9

AA8

A_A10

Y5

A_A11

W7

A_A12

N4

A_A13

W5

A_A14

AB8

A_A15

AA2

A_DQS1

AB1

A_DQS1B

W2

A_DQS0

Y1

A_DQS0B

AA1

A_DM0

W1

A_DM1

N2

A_ODT

N1

A_WE_B

P1

A_CAS_B

P2

A_RAS_B

P3

A_RST_B

M1

A_BA2

V3

A_BA1

M2

A_BA0

T2

A_D0

AB4

A_D1

T1

A_D2

AA5

A_D3

R1

A_D4

AA6

A_D5

R2

A_D6

AB5

A_D7

AA3

A_D8

V1

A_D9

AA4

A_D10

U1

A_D11

AB2

A_D12

U2

A_D13

AB3

A_D14

V2

A_D15

U4

A_VREF

U3

A_PLL33

M5

A_VDDQ

N5

A_VDDQ

P5

A_VDDQ

R5

A_VDDQ

T5

A_VDDQ

U5

A_VDDQ

V5

A_VDDQ

V6

A_VDDQ

V7

A_VDDQ

V8

A_VDDQ

AB7

A_CKE

AB6

A_CK

AA7

A_CKB

8$

$5

RN13

10Rx4

R296

33R

R297

33R

R298

33R

R238

33R

R236

33R

R226

33R

R229

33R

R231

33R

R230

33R

R232

33R

R203

33R

R233

33R

R227

33R

R237

33R

R239

33R

R235

33R

R228

33R

R234

33R

R240

33R

R299

33R

R26

2K_1%

R29

2K_1%

C28

104

R27

2K_1%

C27

NC

C30

104

C29

104

R28

2K_1%

R23

240R/1%

/RST

ODT

BA2

BA0

/CS

BA1

A12/BC#

VREFCA

ZQ

CKE

/CK

CK

/WE

/CAS

/RAS

DQ5

DQ7

DQ4

VREFDQ

/DQSL

DQSL

DQ0

DMU

DML

DQSU

/DQSU

NC

NC

NC

NC

NC

NC

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

A10/AP

A4

A1

A11

A6

A8

A13

A9

A7

A2

A5

A3

A0

VSS

VSS

VSS

VSS

S

S

V

S

S

V

VSS

VSS

VSS

VSS

VSS

VSS

DQ6

DQ2

DQ3

DQ1

DQ8

DQ11 DQ9

DQ10

DQ14

DQ12

DQ15

DQ13

VDD

VDD

VDD

VDD

VDD

VDDQ

VDDQ

VDD

VDD

VDD

VDD

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

9

8

7

3

2

1

T

R

P

N

M

L

K

J

H

G

F

E

D

C

B

A

E3

DQ0

F7

DQ1

F2

DQ2

F8

DQ3

H3

DQ4

H8

DQ5

G2

DQ6

H7

DQ7

D7

DQ8

C3

DQ9

C8

DQ10

C2

DQ11

A7

DQ12

A2

DQ13

B8

DQ14

A3

DQ15

B1

VSSQ

B9

VSSQ

D1

VSSQ

D8

VSSQ

E8

VSSQ

F9

VSSQ

G1

VSSQ

G9

VSSQ

E2

VSSQ

A1

VDDQ

A8

VDDQ

C1

VDDQ

C9

VDDQ

D2

VDDQ

E9

VDDQ

H2

VDDQ

F1

VDDQ

H9

VDDQ

D3

DMU

E7

DML

C7

DQSU

B7

DQSU#

F3

DQSL

G3

DQSL#

N3

A0

P7

A1

P3

A2

N2

A3

P8

A4

P2

A5

R8

A6

R2

A7

T8

A8

R3

A9

L7

A10/AP

R7

A11

N7

A12

M8

VREFCA

B2

VDD

D9

VDD

G7

VDD

K2

VDD

K8

VDD

A9

VSS

B3

VSS

E1

VSS

G8

VSS

J2

VSS

P9

VSS

T1

VSS

K3

CAS#

J3

RAS#

L3

WE#

M2

BA0

N8

BA1

L2

CS#

J7

CK

K7

CK#

L1

NC

M7

NC

T7

A14

J9

NC

K1

ODT

K9

CKE

T3

A13

M3

BA2

H1

VREFDQ

L9

NC

J1

NC

N9

VDD

N1

VDD

R1

VDD

J8

VSS

M1

VSS

M9

VSS

P1

VSS

T2

RESET#

L8

ZQ

R9

VDD

T9

VSS

8

17&&0,3',,

C283

104

C282

10uF

C310

104

C284

104

C285

104

C286

104

C287

104

C288

104

C289

104

C290

104

C291

104

C316

C207

10uF

C314

104

C315

104

C312

104

C311

104

C309

104

C303

104

C302

104

C304

104

C305

104

C306

104

C194

10uF

R22

10K

R65

10R

R66

10R

1

2

3

4

5

6

7

8

RN11

10Rx4

RN15

10Rx4

RN16

10Rx4

RN17

10Rx4

C354

3

C355

100P

C375

3

C299

X)

M15

GND

M14

GND

M13

GND

M12

GND

M11

GND

M10

GND

M9

GND

M8

GND

M7

GND

L16

GND

L15

GND

L14

GND

L13

GND

L12

GND

L11

GND

L10

GND

L9

GND

L8

GND

L7

GND

K15

GND

K14

GND

K13

GND

K12

GND

K11

GND

K10

GND

K9

GND

K8

GND

J14

GND

J13

GND

J12

GND

U9

VDD33

U8

VDD33

U7

VDD33

U6

VDD33

T17

VDD33

T16

VDD33

T6

VDD33

R16

VDD33

R6

VDD33

P16

VDD33

P6

VDD33

N17

VDD33

N16

VDD33

H16

VDD33

H10

VDD33

H9

VDD33

H8

VDD33

H7

VDD33

H6

VDD33

G16

VDD33

G15

VDD33

G14

VDD33

G10

VDD33

F16

VDD33

U12

VDD11

T15

VDD11

T12

VDD11

T11

VDD11

T10

VDD11

T9

VDD11

T8

VDD11

T7

VDD11

R15

VDD11

R14

VDD11

R13

VDD11

R12

VDD11

R7

VDD11

P7

VDD11

K17

VDD11

K16

VDD11

K7

VDD11

J16

VDD11

J15

VDD11

J11

VDD11

J10

VDD11

J7

VDD11

J9

VDD11

J8

VDD11

H15

VDD11

H14

VDD11

H13

VDD11

H12

VDD11

H11

VDD11

Y7

GND

Y4

GND

Y2

GND

W6

GND

W3

GND

T4

GND

R11

GND

R10

GND

R9

GND

R8

GND

R3

GND

P15

GND

P14

GND

P13

GND

P12

GND

P11

GND

P10

GND

P9

GND

P8

GND

N15

GND

N14

GND

N13

GND

N12

GND

N11

GND

N10

GND

N9

GND

N8

GND

N7

GND

N6

GND

N3

GND

M16

GND

G13

PLL_AVDD33

G12

PLLC_AVDD

G11

PLL_AVDD

G17

OTP_V25

8*

$5

[4] A_RMA0

[4] A_RMA1

[4] A_RMA2

[4] A_RMA3

[4] A_RMA4

[4] A_RMA5

[4] A_RMA6

[4] A_RMA7

[4] A_RMA8

[4] A_RMA9

[4] A_RMA10

[4] A_RMA11

[4] A_RMA12

[4] A_RMA13

[4] A_RMA14

[4] A_RMA15

[4]A_RDQS0H

[4]

A_RDQS0H#

[4]A_RDQS0L

[4]

A_RDQS0L#

[4]A_RDQM0L

[4]

A_RDQM0H

[4] A_RODT

[4]

A_RWE

[4] A_RCAS

[4] A_RRAS

[4]A_RRESET

[4] A_RBA2

[4] A_RBA1

[4] A_RBA0

[4]

A_RMD0

[4]

A_RMD1

[4]

A_RMD2

[4]

A_RMD3

[4]

A_RMD4

[4]

A_RMD5

[4]

A_RMD6

[4]

A_RMD7

[4]

A_RMD8

[4]

A_RMD9

[4]

A_RMD10

[4]

A_RMD11

[4]

A_RMD12

[4]

A_RMD13

[4]

A_RMD14

[4]

A_RMD15

[3]

DDR_PLL33

[4]

A_VREF

[3,4]

DDR_1V5

[4]

A_RCKE

[4]

A_RCLK

[4]

A_RCLK#

[3,4]

DDR_1V5

[3,4]

DDR_1V5

[4]

A_VREF

[3,4]

DDR_1V5

[4]

A_RVREF

[3,4]

DDR_1V5

[4]

A_RVREF

[3,4]

DDR_1V5

[3,4]

DDR_1V5

[4]

DDR_D0

[4]

DDR_D1

[4]

DDR_D2

[4]

DDR_D3

[4]

DDR_D4

[4]

DDR_D5

[4]

DDR_D6

[4]

DDR_D7

[4]

DDR_D8

[4]

DDR_D9

[4]

DDR_D10

[4]

DDR_D11

[4]

DDR_D12

[4]

DDR_D13

[4]

DDR_D14

[4]

DDR_D15

[4]

A_RCLK

[4]

A_RCLK#

[4]

A_RCKE

[4]

A_RRESET

[4] A_RMA0

[4] A_RMA1

[4] A_RMA2

[4] A_RMA3

[4] A_RMA4

[4] A_RMA5

[4] A_RMA6

[4] A_RMA7

[4] A_RMA8

[4] A_RMA9

[4] A_RMA10

[4] A_RMA11

[4] A_RMA12

[4] A_RMA13

[4] A_RMA14

[4] A_RMA15

[4] A_RDQM0H

[4] A_RDQM0L

[4]

A_RDQS0H

[4] A_RDQS0H#

[4]

A_RDQS0L

[4] A_RDQS0L#

[4]

A_RODT

[4]

A_RBA0

[4]

A_RBA1

[4]

A_RBA2

[4]

A_RWE

[4]

A_RRAS

[4]

A_RCAS

[4] A_RMD4

[4] A_RMD6

[4] A_RMD2

[4] A_RMD0

[4] A_RMD11

[4] A_RMD13

[4] A_RMD9

[4] A_RMD15

[4]

DDR_D0

[4]

DDR_D1

[4]

DDR_D2

[4]

DDR_D3

[4]

DDR_D4

[4]

DDR_D5

[4]

DDR_D6

[4]

DDR_D7

[4]

DDR_D8

[4]

DDR_D9

[4]

DDR_D10

[4]

DDR_D11

[4]

DDR_D12

[4]

DDR_D13

[4]

DDR_D14

[4]

DDR_D15

[4] A_RMD12

[4] A_RMD8

[4] A_RMD10

[4] A_RMD14

[4] A_RMD1

[4] A_RMD3

[4] A_RMD7

[4] A_RMD5

[3]

AVDD33

[3]

PLL_VDD33

OTP_V25

[3,5]

CORE_1V1

[3]

PLL_1V2

SYS SET

2018/09/12 22:50:21 (GMT+09:00)