NW-HD5

19

19

NW-HD5

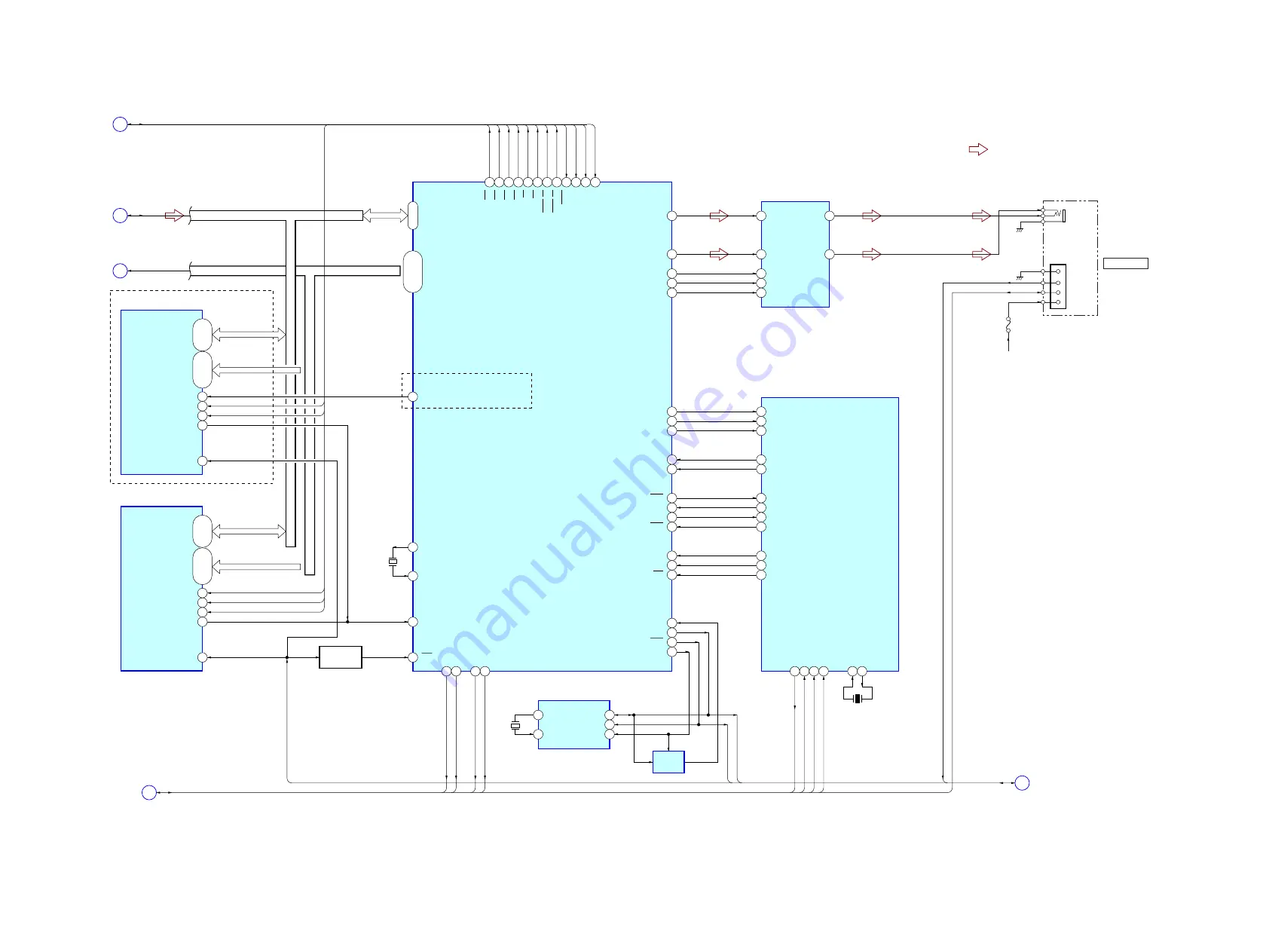

5-2. BLOCK DIAGRAM – MAIN Section (2/2) –

193

PK7/CS7

IC1001_XCS7

182

PJ1/RE

IC1001_XRE

185

PJ4/WE

IC1001_XWE

183

PJ2/LWR/LB

IC1001_XLWR

184

PJ3/UWR/UB

IC1001_XUWR

181

PJ0/WAIT

IC1001_WAIT

88

PG2/DACK1/INT6

XINTREQG

89 83

PG3/DREQ1/INT7

XINTREQH

PF2/EC2/INT4

XINTREQU

38 – 53

PO0/D0 – P07/D7,

PB0/D8 – PB7/D15

PL1/A1 – PL7/A7,

PM0/A8 – PM7/A15,

PN0/A16 – PN7/A23

D0 – 15

D0 – 15

A1 – 20

D0 – 15

IC1003 – IC7001

186

PK0/CS0

IC1001_XCS0

191

PK5/CS5

IC1001_XCS5

192

PK6/CS6

IC1001_XCS6

DATA BUS

B

C

A1 – 23

ADDRESS BUS

FLASH MEMORY

IC1101

D

E

197 – 207,

2 – 13

48, 1 – 9,

16 – 25

A1 – A20

29 – 36,

38 – 45

DQ0 – DQ15

R/XB 15

XWE

IC1001_XUWR

11

XOE

IC1001_XRE

28

XCE

IC1001_XCS0

26

PG0/DAKC0

86

XRST

XRST

12

RST

106

138

137

LEVEL SHIFT

Q1001

AOUTL 134

HEADPHONE AMP

IC4301

MAIN SYSTEM CONTROLLER,

D/A CONVERTER

IC1003 (1/2)

AOUTR 133

PF4/BEEP 85

PR7 163

PR6 162

L-IN

3

R-IN

1

BEEP

14

MUTE

15

HP/L

BEEP

HP_MUTE

HP_LINE_SEL

16

PP1/RB 34

PF2

36

SREQ

LOUT 10

ROUT 12

J4301

F4301

+2.4V_AD

RM_GND

/LINE OUT

RM_KEY

RM_TSB

RM_VDD

i

PP0/RP 33

PQ6 152

PF0

34

NRST

WAKEUP

XRESET

33

PG1/DREQ0/INT5 87

PF0/EC0/INT3 81

PF1

35

PF3

DATA_READY

XINT

37

PC3/SCS0 60

PC2/SI0 59

PC3

42

PC1

SS

SI

40

PC1/SO0 58

PC0/SCK0 57

PC2

41

PC0

SO

SCLK

SUB SYSTEM

CONTROLLER

IC3001

38

PI1/ADDT 172

P10/PCMD0

15

PI2/LRCK 173

PI3/BCK 174

P12/LRCK0

14

P13/BCK0

GDAC_LRCK

GDAC_PCM0

GDAC_BCK

13

PE6/SI1 75

PE5/SO1 74

PE4/SCK1 73

PE7/SCS1

MULTI_SCK

PMC_DTCK

AD_RMKEY

MULTI_SO

76

SIO 1

REAL TIME CLOCK

IC9503

X9501

32kHz

SCLK 2

CE 12

BUFFER

IC9502

77

XOUT/CK0

175

P14/FS256

151

PQ5

153

PQ7

XRESET

SLEEP

FS256

XOUT

12

PF4/XRDE

4

CDIF_PCMD

CDIF_XRDE

2

BCK

1

LRCK

CDIF_LRCK

CDIF_BCK

30

XTAL

29

EXTAL

OSC OUT

8

OSC IN

7

G

PCMD

A1 – 23

X1002

22.5792MHz

XTAL

EXTAL

X3001

22.5792MHz

• SIGNAL PATH

: AUDIO

IC3001 – IC7001

MULTI_SIO

A1 – 20

IC1001_XRE

D0 – 15

48, 1 – 9,

16 – 25

A1 – A20

29 – 36,

38 – 45

DQ0 – DQ15

R/XB 15

XWE

IC1001_XUWR

11

XOE 28

XCE 26

XRST 12

187 GAND_XCS1

(E, Taiwan, Korean, Chinese, Tourist)

(E, Taiwan, Korean, Chinese, Tourist)

FLASH MEMORY

IC1102

(Page 18)

(Page 18)

(Page 18)

(Page 18)

(Page 20)

Ver. 1.3