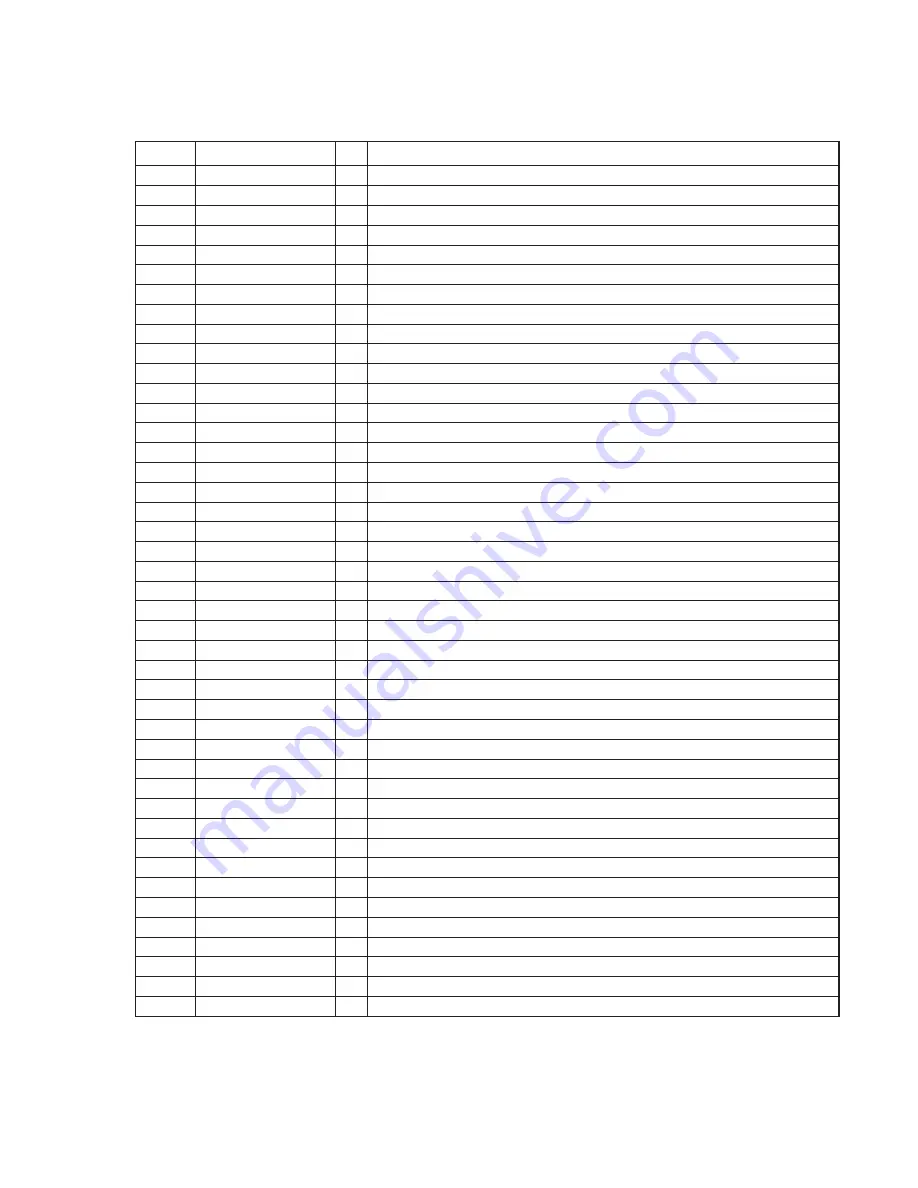

– 11 –

Pin No.

Pin name

I/O

Description

1 – 3

SEG 12–14

O

LCD segment signal output terminal.

4

FP26

–

Not used (Open).

5

XRST– DSP

O

Reset output terminal.

6

AMUTE – HP

O

Audio mute output terminal.

7

XOE-ESP

O

ESP POWER ON control output.

8

C2PO FILTER

–

Not used (Open).

9

DACLT–DAC

I/O

CPU serial data input, latch signal output (For DAC only).

10

C2POEN

O

C2PO signal control output. “ L ” : Stop “ H ” : Searching

11

TEOADJ – TEO

O

Tracking ADJ switch control output.

12

RMDAT–WRMT

O

Serial data output to LCD remote controller.

13

VLCD (GND)

–

Connect to ground.

14

VSS (GND)

–

Connect to ground.

15

NDLY (GND)

–

Connect to ground.

16

CHGON – PWR

O

Charge ON/OFF control output.

17

PCON–PWR

O

Power ON/OFF control output. “ L ” : ON “ H ” : OFF

18

XMCRST–PWR

I

System reset input terminal.

19

OSC 1

I

System clock oscillator input terminal (4.1943 MHz).

20

OSC 2

O

System clock oscillator output terminal (4.1943 MHz).

21

SDT–ESP

I

Serial data input from ESP control (IC601).

22

SDT–ESP

O

Serial data output to ESP control (IC601).

23

SCK–ESP

O

Serial clock output to ESP control (IC601).

24

XBBSW – DBB

O

DBB switch control output.

25

XLT–ESP

O

Latch signal output to ESP control (IC601).

26

HOLD–SW

I

Hold switch input termianl. “ L ” : HOLD ON “ H ” : HOLD OFF

27

XLMT–MD

I

Limit switch input terminal. “ L ” : Inside Track

28

XRSM–SW

I

RESUME switch input terminal. “ L ” : ON “ H ” : OFF

29

WP XDC–DT PWR

I

DC in voltage detection terminal.

30

WP XOPEN–SW

I

Door open switch input terminal. “ L ” : Close “ H ” : Open

31

WP XPLAY–SW

I

Play/pause key input terminal.

32

WP RMKEY WRMT

I

Remote control key input terminal.

33

XL/O DCT

I

LINE OUT jack detection terminal. “ L ” : Present “ H ” : No

34

XRCHG–SW

I

Rechargeable battery detection terminal. “ L ” : Present “ H ” : No

35

XAVLS–SW

I

AVLS switch input terminal.

36

R/W DSP

O

Read/Write switching signal output terminal. “ L ” : Read “ H ” : Write

37

SDT–DSP

I

SUB–Q signal input terminal.

38

SDT–DSP

O

Serial data output to DSP (IC502) and D/A C (IC301).

39

SCK–DSP

O

Clock signal to enter SUB–Q signal to DSP (IC502) and D/A C (IC301).

40

FOK–RF

I

FOK signal input terminal.

41

BUSY–DSP

I

BUSY signal input terminal from DSP (IC502).

42

BEEP–H/P

O

Beep sound output terminal.

43

INT SCOR–DSP

I

Sub code sync SO+SI input terminal.

44

INT DFCT RF

I

Wireless remote control signal input.

45

VDD (VCPU)

–

Power supply terminal.

SECTION 6

DIAGRAMS

6-1. EXPLANATION OF IC TERMINALS

IC801 MC68HC05L15SC442720CPB (SYSTEM CONTROL)