3-2

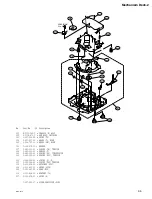

CDP-D12

Diode, IC

[DIODE]

2A02

2A02M

R/

B

OUT

V

CC

CS

IN

SK

IN

1

2

3

4

8

7

6

5

WC

IN

GND

DO

OUT

DI

IN

4 K (256

x

16)-BIT EEPROM

—TOP VIEW—

INPUTS

CS

DI

SK

WC

OUTPUTS

DO

R/

B

: CHIP SELECT

: OPERATING CODE, ADDRESS, AND SREIAL DATA

: SERIAL DATA CLOCK

: WRITE CONTROL

: SERIAL DATA

: READY/

BUSY

STATUS SIGNAL

8

CS

1

SK

8

DI

3

DO

4

5

6

ADDRESS

BUFFER

8

ADDRESS

DECODER

4,096-BIT

EEPROM

ARRAY

HIGH VOLTAGE

GENERATOR

POWER SUUPLY

VOLTAGE DETECTOR

WRITE

DISABLE

COMMAND

REGISTER

COMMAND CODE

CONTROL

CLOCK GENERATION

16

DATA

REGISTER

16

R/W

AMPLIFIER

R/

B

WC

1

2

3

4

8

7

6

5

ICLK

V

CC

GND

S0

CLK

CLK/2

OE

S1

PLL CLOCK DIVIDER

—TOP VIEW—

INPUTS

OE

ICLK

S0, S1

OUTPUTS

CLK, CLK/2

: OUTPUT ENABLE

: CLOCK

: SELECT FOR OUTPUT CLOCK

: CLOCK

DIVIDER

AND

SELECTION

CIRCUITRY

ICLK

1

S1

S0

4

5

/2

CLK

CLK/2

8

7

BR9040F-WE2 (ROHM)

ICS541MT (ICS)

EMITTER

CPT-230S-C-TD-BC (SANYO)

[IC]

1

2

3

4

5

6

7

8

MCLK

BICK

SDTI

LRCK

PDN

CSN

CCLK

CDTI

16

15

14

13

12

11

10

9

DZFL

DZFR

V

CC

GND

AOUTL

+

AOUTL

_

AOUTR

+

AOUTR

_

2-CHANNEL AUDIO D/A CONVERTER

—TOP VIEW—

INPUTS

BICK

CCLK

CDTI

CSN

LRCK

MCLK

PDN

SDTI

OUTPUTS

AOUTL

+

AOUTL

_

AOUTR

+

AOUTR

_

DZFL

DZFR

: AUDIO SERIAL DATA CLOCK

: CONTROL DATA

: CONTROL DATA IN SERIAL MODE

: CHIP SELECT

: L/R CLOCK

: MASTER CLOCK

: POWER DOWN MODE

: AUDIO SERIAL DATA

: L-CHANNEL POSITIVE ANALOG

: L-CHANNEL NEGATIVE ANALOG

: R-CHANNEL POSITIVE ANALOG

: R-CHANNEL NEGATIVE ANALOG

: L-CHANNEL DATA ZERO DETECT

: R-CHANNEL DATA ZERO DETECT

CDTI

CCLK

CSN

8

7

6

u

P

INTERFACE

DE-EMPHASIS

CONTROL

CLOCK

DIVIDER

SDTI

BICK

LRCK

4

2

3

AUDIO

DATA

INTERFACE

MCLK

8

X

INTERPOLATOR

∆Σ

MODULATOR

SCF

8

X

INTERPOLATOR

∆Σ

MODULATOR

SCF

AOUTL

+

AOUTL

_

AOUTR

+

AOUTR

_

1

12

11

10

9

AK4382AVT-E2 (AKM)

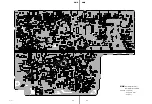

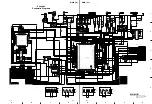

Summary of Contents for CDP-D12

Page 1: ...COMPACT DISC PLAYER CDP D12 SERVICE MANUAL 1st Edition ...

Page 4: ......

Page 34: ......

Page 42: ......

Page 48: ......

Page 54: ...Printed in Japan Sony Corporation 2003 10 16 2003 CDP D12 UC CE CN E 9 976 920 01 ...