— 23 —

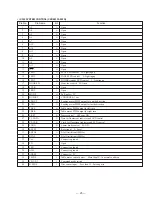

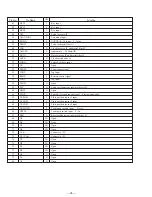

Pin Name

DV

DD

ASYE

PSSL

WDCK

LRCK

DATA

BCLK

64DATA

64BCLK

64LRCK

GTOP

XUGF

XPLCK

GFS

PFCK

C2PO

XRAOF

MNT3

MNT2

MNT1

MNT0

XTAI

XTAO

XTSL

DVss

FSTI

FSTO

FSOF

C16M

MD2

DOUT

EMPH

WFCK

SCOR

SBSO

EXCK

SUBQ

SQCK

MUTE

SENS

Pin No.

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

I/O

–

I

I

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

I

O

I

–

I

O

O

O

I

O

O

O

O

O

I

O

I

I

O

Function

Digital power supply

Asymmetry circuit ON/OFF (Connected to +5V)

Audio data output mode selection input (Connected to Ground)

48-bit slot D/A interface. Word clock. (Open)

48-bit slot D/A interface. LR clock.

DA 16 output when PSSL=1.48-bit slot serial data when PSSL=0

DA 15 output when PSSL=1.48-bit slot data when PSSL=0

DA 14 output when PSSL=1.64-bit slot data when PSSL=0 (Open)

DA 13 output when PSSL=1.64-bit slot data when PSSL=0 (Open)

DA 12 output when PSSL=1.64-bit slot data when PSSL=0 (Open)

DA 11 output when PSSL=1.GTOP output when PSSL=0 (Open)

DA 10 output when PSSL=1.XUGF output when PSSL=0 (Open)

DA 09 output when PSSL=1.XPLCK output when PSSL=0 (Open)

DA 08 output when PSSL=1.GFS output when PSSL=0 (Open)

DA 07 output when PSSL=1.RFCK output when PSSL=0 (Open)

DA 06 output when PSSL=1.C2PO output when PSSL=0 (Open)

DA 05 output when PSSL=1.XRA0F output when PSSL=0 (Open)

DA 04 output when PSSL=1.MNT3 output when PSSL=0 (Open)

DA 03 output when PSSL=1.MNT2 output when PSSL=0 (Open)

DA 02 output when PSSL=1.MNT1 output when PSSL=0 (Open)

DA 01 output when PSSL=1.MNT0 output when PSSL=0 (Open)

X'tal oscillator circuit input

X'tal oscillator circuit output (Open)

X'tal selection input pin (Connected to Ground)

Digital Ground

Clock input for digital servo block

2/3 divider output of pins 62, 63

1/4 divider output of pins 62, 63 (Open)

16.9344 MHz output (Open)

Digital-out ON/OFF control pin (Connected to +5V)

Digital-out output pin (Open)

Playback disc output in emphasis mode (Open)

WFCK output (Open)

Sub-code sync output

Sub-P through Sub-W serial output (Open)

Clock input for SBSO read-out (Connected to Ground via a 10 k

Ω

)

Sub-Q 80-bit output

Clock input for SQSO read-out

Muting selection pin

SENS output

• Abbreviation

WFCK: Wirte Frame Clock

Summary of Contents for CDP-CX200

Page 5: ... 5 PX This section is extracted from instruction manual ...

Page 6: ... 6 ...

Page 7: ... 7 ...

Page 8: ... 8 ...

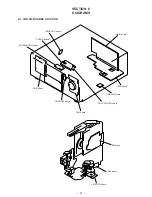

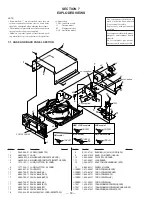

Page 11: ... 11 3 5 BASE UNIT ASSEMBLY 1 Screw BVTT3x6 2 Fulcrum plate BU UPPER assy 3 Base unit ...

Page 27: ......

Page 28: ......

Page 29: ......

Page 30: ......

Page 31: ......

Page 32: ......

Page 48: ......

Page 49: ......

Page 50: ......

Page 51: ......

Page 52: ......

Page 53: ......

Page 54: ......

Page 55: ......

Page 56: ......

Page 57: ......

Page 58: ......

Page 59: ......

Page 60: ......

Page 61: ......

Page 62: ......

Page 63: ......

Page 64: ......

Page 65: ......

Page 66: ......

Page 67: ......