Field Programmable Gate Array Registers

http://www.motorola.com/computer/literature

3-17

3

IRQ Enable Register

The IRQ Enable Register (IRQEN) defines the events that can generate an

IRQ. The IRQ generated is set by IRQ Select Register (IRQNUM). Refer

to

SMB (Bit 0)

❏

Set to a logic 1 to allow the generation of an IRQ when the SMB

Alert is active.

❏

Write a logic 0 to this bit to disable an IRQ for this event.

TEMP (Bit 1)

❏

Set to a logic 1 to allow the generation of an IRQ when TEMP is

active.

❏

Write a logic 0 to this bit to disable an IRQ for this event.

ALARM_A (Bit 3) and ALARM_B (Bit 2)

❏

Set to a logic 1 to allow the generation of an IRQ when the

ALARM_A or ALARM_B go active.

❏

Write a logic 0 to this bit to disable an IRQ for this event.

ENUM (Bit 4)

❏

Set to a logic 1 to allow the generation of an IRQ when the ENUM

event occurs.

❏

Write a logic 0 to this bit to disable an IRQ for this event.

ENABLE (Bit 7)

❏

Set to a logic 1 to allow the listed events to generate an IRQ.

❏

Write a logic 0 to prevent the events from generating an IRQ.

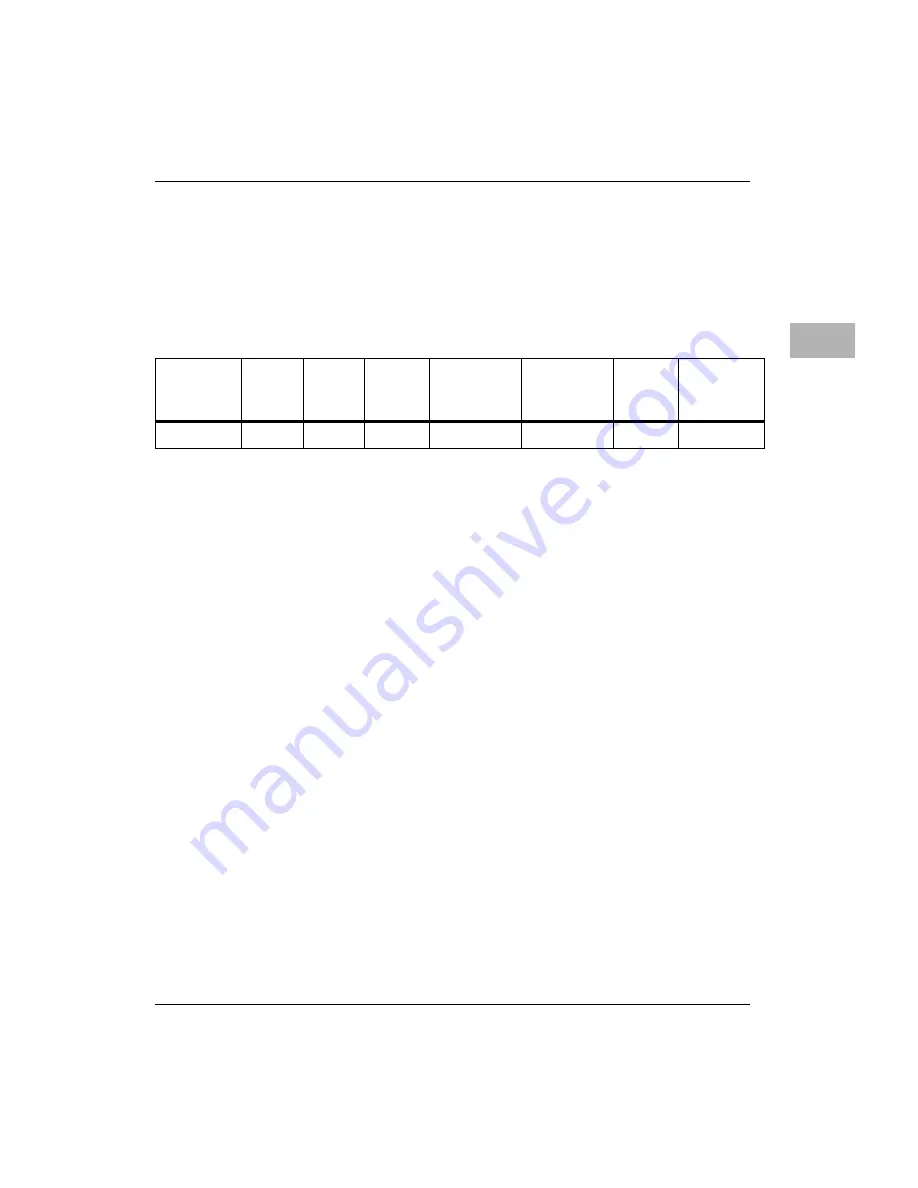

Table 3-15. Bit descriptions for the IRQEN register

7 (most

significant

bit)

6

5

4

3

2

1

0 (least

significant

bit)

ENABLE

RES

RES

ENUM

ALARM_A

ALARM_B

TEMP

SMB

Solution Systems Technologies Inc.

720-565-5995 | [email protected] | www.solusys.com

Solution Systems Technologies Inc.

720-565-5995 | [email protected] | www.solusys.com